На сегодняшний день производители памяти превзошли сами себя по рекордам скорости для памяти DDR4. Однако, до того как преемник DDR5 доберется до конечного потребителя, потребуется некоторое время. Пока окончательные спецификации планируется опубликовать летом 2018 года. Самая важная особенность DDR5: удвоенная пропускная способность памяти по сравнению с DDR4.

На сегодняшний день производители памяти превзошли сами себя по рекордам скорости для памяти DDR4. Однако, до того как преемник DDR5 доберется до конечного потребителя, потребуется некоторое время. Пока окончательные спецификации планируется опубликовать летом 2018 года. Самая важная особенность DDR5: удвоенная пропускная способность памяти по сравнению с DDR4.

Представитель ассоциации технических спцециалистов JEDEC работает над этими спецификациями и регулярно представляет свои собственные результаты. Тем не менее, более подробной информации, чем удвоенная пропускная способность памяти при том же энергопотреблении, сейчас нет.

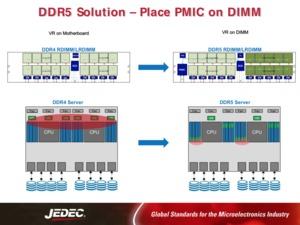

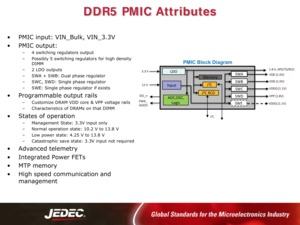

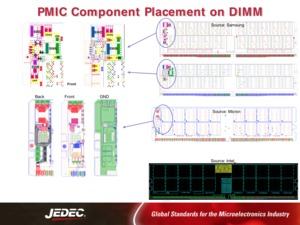

Модули памяти имеют собственный источник питания - по крайней мере, так говорит план компании Integrated Device Technology, которая поставляет различные полупроводниковые компоненты. Среди прочего, компоненты из IDT используются на модулях памяти. Для памяти DDR5 планируется использовать PMIC (Power Management Integrated Circuits)

.

Теперь управление питанием больше не выполняется непосредственно через материнскую плату - она только обеспечивает напряжение питания, которое затем преобразует PMIC. Как обычно, для питания используется уровень напряжения в 12 В, который затем уменьшается до 1 В для микросхем памяти (1,2 В для DDR4, 1,5 В для DDR3, 1,35 В для DDR3L). Опорное напряжение для сигналов данных (VDDQ) должно быть 1,1 В. Напряжение 1,8 В доступно для других компонентов на модуле памяти.

IDT предполагает, что такой подход обеспечит большую стабильность работы источника питания. То же самое относится к источнику питания в случае пиковых токов. Кроме того, сохраняется свободное пространство на материнских платах, которое может быть использовано для большего количества слотов DIMM. Количество слотов для модулей памяти может быть увеличено с 24 до 32, что, конечно, также влияет на общую конфигурацию памяти. Плюс ко всему, больше нет необходимости в оснащении материнских плат источником питания с учетом максимальной конфигурации, каждый модуль DIMM можно будет сконфигурировать отдельно. Это сделало дизайн более гибким.

DDR5 также приносит улучшения в других областях. В то время как DDR4 использует шину памяти шириной 72 бит, 64 бита которых могут использоваться для пользовательских а данных и 8 бит для кода исправления ошибок (ECC), в DDR5 установлена ширина для ECC 16 бит, которая предлагает дополнительные опции для исправления ошибок. Кроме того, появляется преемник интерфейса I2C в лице I3C.

Ещё пройдёт некоторое время, прежде чем мы увидим DDR5 в серверах и компьютерах конечных пользователей, как уже упоминалось ранее. Однако подход к установке питания и напряжения на самих модулях мы сможем увидеть только в серверах.