Страница 2: Архитектура Zen 2

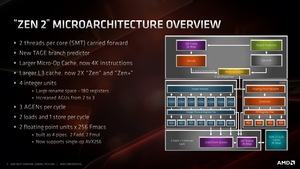

Кристаллы на основе архитектуры Zen 2 имеют внутреннее название Valhalla. Кристалл Valhalla, также называемый как CCD (Core Complex Die), состоит из двух блоков Core Complexes (CCX), каждый по четыре ядра. В результате кристалл Valhalla может содержать, максимум, восемь ядер. Поддержка SMT не изменилась, каждое ядро может выполнять два потока.

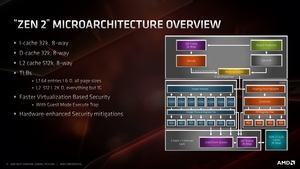

Каждый блок CCX оснащен 16 Мбайт кэша L3, который разделен на четыре участка по 4 Мбайт. Каждое ядро имеет доступ к собственным 512 кбайт кэша L2. Кэш L1 состоит из 32 кбайт для инструкций и 32 кбайт для данных. Также AMD добавила новые инструкции работы с кэшем, которые должны увеличить эффективность обработки.

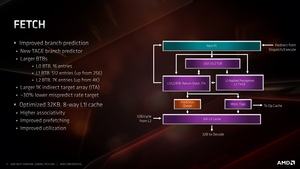

Значительную роль в улучшении IPC является новый предсказатель ветвлений. Эффективное предсказание ветвлений позволяет более полно задействовать все ступени конвейера. Процессор предсказывает дальнейшие вычисления, которые произойдут вероятнее всего. Прогноз может сбыться, но CPU может и ошибиться. В итоге от доли успешных предсказаний зависит эффективность работы процессора. AMD с процессорами Zen 2 использует новый блок предсказания TAGE, где TAGE как раз описывает один из возможных алгоритмов.

Предсказатель ветвлений TAGE можно назвать гибридным. То есть вместо одного вероятного пути дальнейших вычислений рассчитываются несколько. У каждого сработавшего ветвления повышается приоритет, более приоритетные ветвления будут затем рассчитываться первыми. Буфер предсказания ветвлений TAGE довольно большой, и нем хранятся не отдельные ветвления, а их дерево. На данный момент предсказание ветвлений TAGE считается одним из самых эффективных.

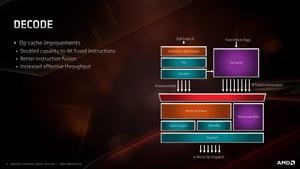

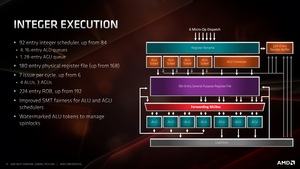

Кэш микроопераций теперь может содержать в два раза больше инструкций. В случае Zen 2 число инструкций составляет 4K, у процессоров Zen и Zen+ буфер был всего 2K. AMD увеличила число блоков генерации адресов Address Generation Units (AGU) с двух до трех.

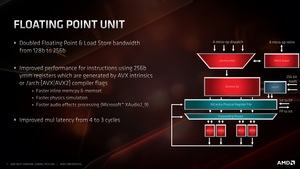

Весьма интересны два 256-битных блока работы с плавающей запятой, которые теперь могут обрабатывать инструкции AVX256. За такт теперь могут выполняться две операции чтения и одна записи, что позволит быстрее наполнять вычислительные блоки данными.

Кэш данных L1 может обмениваться информацией с кэшем L2 со скоростью 32 байт/такт в обоих направления. В случае кэша инструкций они могут считываться из кэша L2 со скоростью 32 байт/такт. Кэш L2, в свою очередь, может считывать или записывать данные из кэша L2 со скоростью 32 байта/такт. Кэш L3 был увеличен, чтобы минимизировать внешние запросы через Infinity Fabric.

AMD не только увеличила кэши, но и соответствующие регистры. L1 BTB теперь хранит 512 записей вместо 256. В случае L2 BTB размер увеличился с 4K до 7K.

Что касается работы с числами с плавающей запятой, мы уже отметили выше два 256-битных блока. Задержка умножения была снижена с четырех до трех тактов.

Есть ряд улучшений по целочисленным вычислениям. Планировщик Integer Scheduler теперь содержит 92 записи вместо 84. Файл регистров общего назначения был увеличен со 168 до 180 записей. Вместо шести теперь поддерживаются до семи операций выдачи за такт (четыре ALU, три AGU).