Страница 2: Архитектура Zen 3

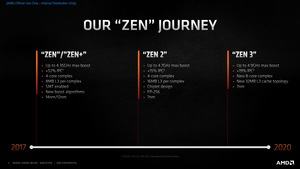

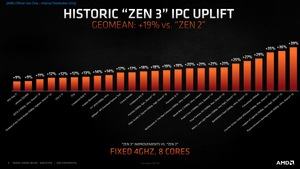

Архитектура Zen/Zen+ стала первым важным шагом для AMD, который принес 52% по производительности в расчете на такт (IPC). Zen 2 оказалась промежуточным этапом по улучшениям, которые не были реализованы в Zen/Zen+, но позволили AMD и дальше нарастить производительность. Прирост IPC 15%, техпроцесс 7 нм и частота Boost до 4,7 ГГц - вот плоды усилий AMD и правильно выбранного дизайна на чиплетах. В итоге AMD сравнялась с Intel, особенно в многопоточных приложениях, что подтверждают бесчисленные тесты.

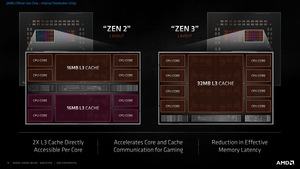

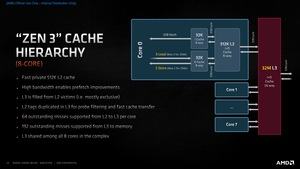

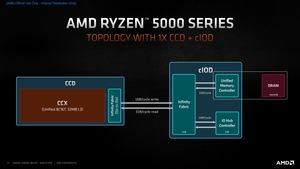

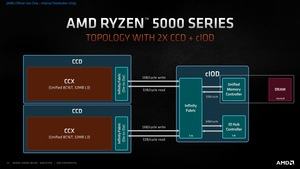

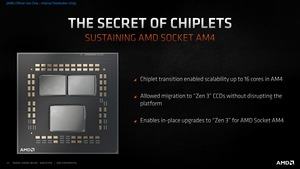

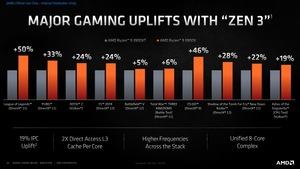

Между Zen/Zen+ и Zen 2 сходств довольно много, но AMD описывает Zen 3 как первую полностью новую разработку после первого поколения Zen. Конечно, многое в архитектурах выглядит очень похоже, но если приглядеться, то будут заметны улучшения во многих деталях и фундаментальные изменения. Центральным компонентом является новый 8-ядерный Core Complex (CCX), который содержит общий кэш L3 32 Мбайт, таких CCX в корпусировке может быть несколько. Кристалл по-прежнему производится по 7-нм техпроцессу, хотя AMD говорит об увеличении тактовых частот из-за оптимизаций дизайна и небольших доработках техпроцесса.

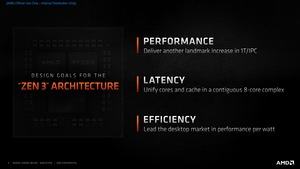

При разработке Zen 3 были поставлены три цели:

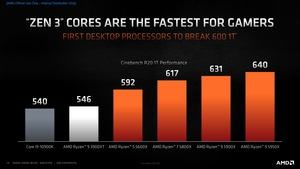

- Производительность: существенный прирост 1T/IPC (однопоточной производительности, в расчете на такт)

- 8-ядерный дизайн CCX для снижения задержек к единому уровню

- При прежнем энергопотреблении оба упомянутых пункта увеличивают эффективность

Обзор архитектуры Zen 3

Ниже мы рассмотрим архитектуру Zen 3 более подробно.

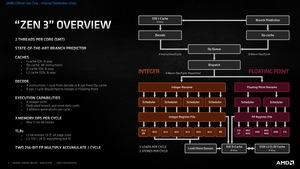

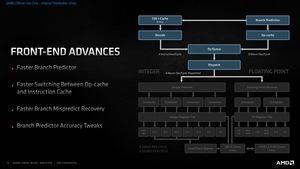

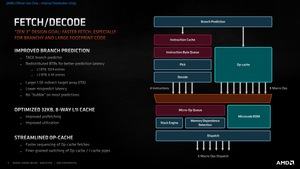

Ядро Zen 3 может по-прежнему выполнять два потока (SMT2). В начале конвейера, как и у всех современных архитектур, имеется блок предсказания ветвлений Branch Predictor. Блок незаменим, чтобы полностью задействовать конвейер и вычислительные блоки. Без предсказания ветвлений современные процессоры были бы заметно медленнее. Впрочем, данный блок одновременно является и "проклятием" архитектур, поскольку многие "дыры" в безопасности были связаны именно с его работой. Эксплойты позволяли получить несанкционированный доступ к данным.

AMD и Intel продолжают улучшать алгоритмы предсказания ветвлений. По сути, речь идет о прогнозе, какая команда будет выполняться следующей, чтобы можно было выполнить ее заранее, даже не зная результат текущей операции. С помощью различных алгоритмов можно определить вероятность той или иной команды. Конечно, здесь все зависит от сценариев использования. В некоторых приложениях точность предсказания ветвлений может достигать 98%, в других не превышает 50%. Соответственно, вычислительная производительность ядер тоже зависит от того или иного приложения.

Важна не только точность предсказания, но и количество ветвлений. С архитектурой Zen 3 AMD может выполнять больше предсказаний ветвлений за такт. В результате в случае ошибочного предсказания системе не нужно возвращаться к предыдущему состоянию, а просто выбрать другой вариант. AMD также снизила задержки данного процесса.

За блоком Branch Predictor видны два способа поступления инструкций непосредственно на само ядро. А именно кэш инструкций L1 на 32 кбайт, который подает на декодер x86 четыре инструкции за такт. Кэш инструкций тоже подвергся оптимизации, чтобы увеличить производительность. Затем инструкции хранятся в очереди операций (Op Queue). Если инструкции используются повторно, их можно сохранить в кэше операций (Op Cache), который способен отдавать в очередь команд восемь макро-операций за такт. Диспетчер (Dispatcher) определяет, какие инструкции или макро-операции будут распределены по целочисленным конвейерам или блокам с плавающей запятой. В случае Zen/Zen+ и Zen 2 AMD обнаружила ряд неэффективных процессов, которые замедляли диспетчер при поступлении двух потоков инструкций (x86 и макро-операции), теперь они устранены.

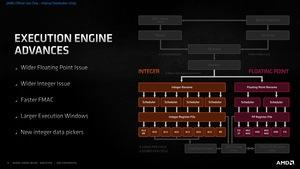

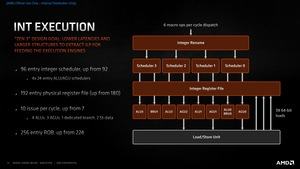

По-прежнему используются четыре целочисленных блока с восемью конвейерами, оснащенными отдельными блоками ветвления и хранения, в итоге пропускная способность целочисленных вычислений значительно увеличилась. Целочисленный планировщик (scheduler) был расширен с 92 до 96 записей, он разделяется на 4x планировщика по 24 записи AKU/AGU. Файл регистров был увеличен со 180 до 192 записи. За такт теперь выполняется десять операций (4x ALUs, 3x AGUs, 1x Branch, 2x Store) вместо семи ранее.

По-прежнему остаются четыре блока ALU и три AGU, но они частично используют ресурсы с блоками Branch и Store. При прежнем количестве арифметических блоков AMD удалось увеличить вычислительную производительность. AMD динамически балансирует нагрузку целочисленных блоков, что улучшает эффективность. Здесь причина как раз кроется в общих ресурсах с блоками Branch и Store. В итоге нужный набор вычислений можно выполнять наиболее оптимально и параллельно.

Что касается работы с плавающей запятой, то число арифметических блоков увеличено до шести. Отдельные блоки (MUL, ADD, MAC) были переделаны так, чтобы дать большую "ширину", чтобы лучше распределять инструкции. Есть отдельные блоки сохранения (Store) и работы с файлом регистров с плавающей запятой (F2I). Здесь AMD тоже попыталась добиться баланса, чтобы пропускная способность некоторых вычислений была выше. Zen 3 может выполнять две 256-битные операции умножения-сложения (FMAC) быстрее. Zen 2 требовалось пять тактов, Zen 3 - только четыре.

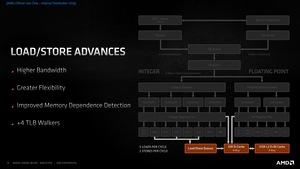

В архитектуре Zen 2 за такт выполнялись только три операции чтения/записи - две загрузки (Load) и одна сохранения (Store). В случае Zen 3 за такт возможны три загрузки и два сохранения. Прирост 33% и 50%, соответственно, тоже хорошо сказывается на производительности.

Также очередь сохранения (Store Queue) была увеличена с 48 до 64 записей. Кэш данных L1 сохранился на уровне 32 кбайт (как и кэш инструкций L1), но теперь за такт поддерживается в три раза больше операций работы с ним. За такт возможны три операции загрузки и две операции сохранения для одного набора данных. Но если набор данных 256-битный (с плавающей запятой), то число загрузок уменьшается до двух, а сохранений - до одной.

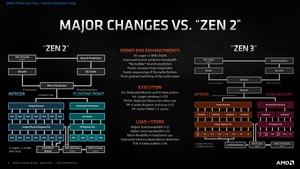

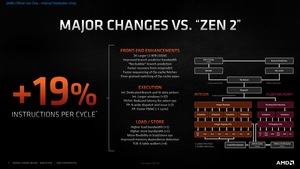

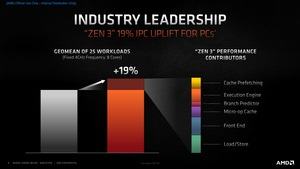

Zen 2 против Zen 3

Если посмотреть на изменения архитектуры в целом, то буфер Branch Target Buffer (BTB) теперь в два раза крупнее. Также была улучшена фронтальная часть конвейера по пропускной способности предсказаний ветвления, улучшена обработка ошибочных предсказаний ветвлений, также быстрее работает коммутация между входящими потоками декодированных инструкций x86 и микро-операций.

Что касается исполнительных блоков, в целочисленном конвейере есть выделенные блоки ветвления и сохранения. Что должно увеличить пропускную способность целочисленной части конвейера. Задержки тоже уменьшились. Что касается операций с плавающей запятой, то число блоков увеличилось с четырех до шести, операции Floating Point Multiply-Accumulate (MAC) были ускорены на такт.

В системе Load/Store произошли изменения: добавилась одна операция загрузки и одна сохранения за такт. Что должно увеличить пропускную способность работы с памятью. В буфере Translation Lookaside Buffer (TLB) теперь поддерживается поиск шести указателей вместо двух.