Чуть раньше в этом году Samsung представила HBM PIM, первую память HBM с интегрированным движком ИИ. Некоторые детали уже были известны, но на конференции Hot Chips корейский производитель раскрыл новые подробности, в том числе и цели разработки подобной памяти. Samsung уже оснащает первые продукты данным видом памяти, а также проводит тесты с потенциальными клиентами.

Чуть раньше в этом году Samsung представила HBM PIM, первую память HBM с интегрированным движком ИИ. Некоторые детали уже были известны, но на конференции Hot Chips корейский производитель раскрыл новые подробности, в том числе и цели разработки подобной памяти. Samsung уже оснащает первые продукты данным видом памяти, а также проводит тесты с потенциальными клиентами.

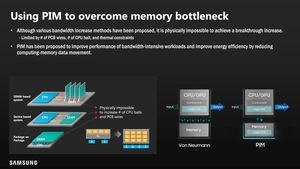

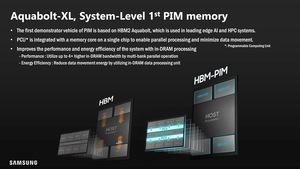

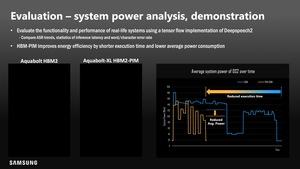

Память Aquabolt-XL относится к типу HBM2 с возможностью вычислений-на-памяти (processing-in-memory, PIM). Подобная память интересна для сценариев машинного обучения/искусственного интеллекта и высокопроизводительных вычислений HPC, поскольку данные можно подготовить к дальнейшим вычислениями напрямую на памяти. Здесь важным преимуществом является очень близкое расположение вычислительного блока и памяти.

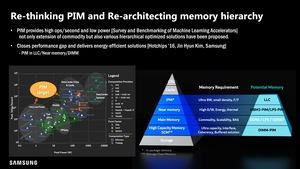

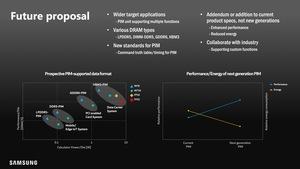

Как считает Samsung, PIM - еще один уровень в иерархии памяти. GPU и CPU имеют кэши, за ними располагается близлежащая память (HBM, GDDR), которую также называют кэшем последнего уровня LLC. Затем следует оперативная память, которая является когерентной для всех подключенных к ней узлов. PIM располагается между LLC и оперативной памятью, где она лучше всего демонстрирует свои преимущества. Samsung пока что работает над HBM2 PIM, но в будущем должны выйти варианты HBM3 PIM, а также версии LPDDR и DDR с поддержкой PIM.

Память PIM важна там, где требуется высокая эффективность вычислений, а также есть возможность повышения производительности путем предварительной обработки данных в памяти.

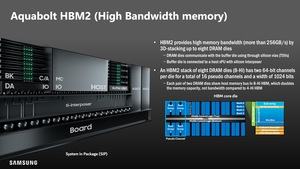

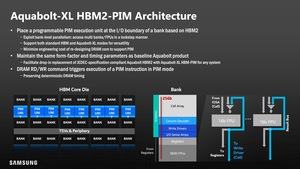

Samsung более подробно раскрыла структуру HBM2 PIM. Некоторые подробности мы уже знаем, к ним добавились новые.

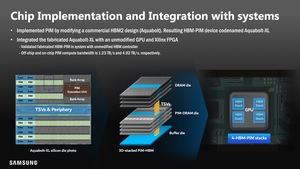

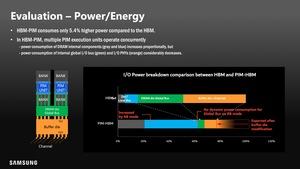

Например, Samsung использует буферный кристалл для HBM2 PIM, четыре слоя памяти с вычислительными блоками (FIMDRAM) и еще четыре слоя классической памяти HBM2 (DRAM). Буферный кристалл напрямую подключается к host-процессору (которым может быть FPGA или GPU) через кремниевую подложку. Соединение буферного слоя, слоев FIMDRAM и DRAM осуществляется через каналы TSV.

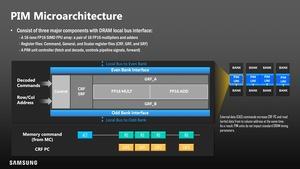

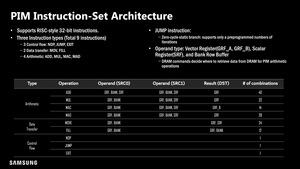

Каждый слой FIMDRAM содержит 32 вычислительных ядра. Они организованы в 16 линий по два вычислительных блока FP16 каждая. Вычислительная производительность чипа с четырьмя слоями FIMDRAM составляет 4 x 32 x 32 байта x 300 МГц= 1,2 TFLOPS для вычислений FP16. Конечно, для работы с вычислительными ядрами необходим набор инструкций, поддерживаются 32-битные команды RISC.

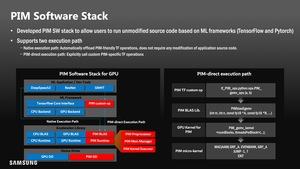

HBM2 PIM может работать в разных режимах. Во-первых, как классическая память HBM2 без какой-либо потери пропускной способности. Во-вторых, можно выделять области памяти для PIM, которые будут использоваться для предварительной обработки данных. При этом пропускная способность тоже не будет страдать, поскольку так называемые псевдоканалы все равно обеспечат высокую скорость, пусть даже некоторые области памяти придется исключить.

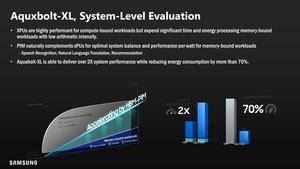

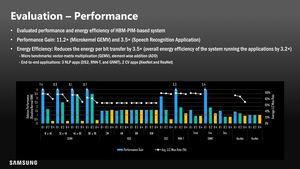

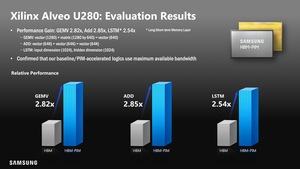

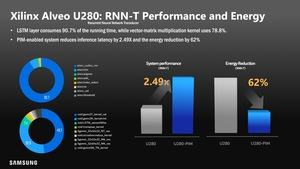

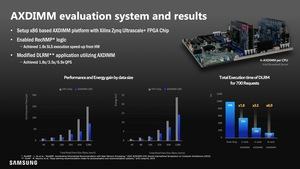

Память Aquabolt -XL, первая представительница HBM2 PIM, тестировалась с Xilinx FPGA. Со стороны FPGA не потребовалось как-либо дорабатывать контроллер памяти HBM. С четырьмя стеками HBM2 PIM (и 4.096-битным интерфейсом памяти) пропускная способность осталась на 1,23 Тбайт/с. Что касается внутренней работы чипа, то есть самой памяти HBM2 PIM, пропускная способность составила 4,92 Тбайт/с.

В зависимости от приложений и параметров, производительность Xilinx Alveo U280 удалось увеличить в 2,5-2,8 раза. Samsung также указывает и более высокий прирост в некоторых других случаях. Эффективность энергопотребления тоже значительно увеличивается, Samsung говорит о приросте до 70%. Однако сама по себе Aquabolt XL потребляет на 5,4% больше классической HBM2 без вычислительных блоков.

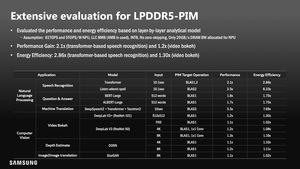

Следующим шагом будет расширение PIM на другие типы памяти. В частности, Samsung говорит о LPDDR5 PIM. Также планируются DIMM PIM. Но конкретных анонсов продуктов HBM2 PIM пока не было.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).