Недавно JEDEC опубликовала обновление спецификаций HBM3. На их основе SK Hynix подготовила презентацию в рамках конференции ISSCC 2022, здесь мы поделимся наиболее важной информацией. После первого поколения память HBM развивалась весьма неспешно вплоть до улучшенной версии второго поколения HBM2E. Конечно, пропускная способность возрастала, но революционного прогресса по емкости и скорости не было.

Недавно JEDEC опубликовала обновление спецификаций HBM3. На их основе SK Hynix подготовила презентацию в рамках конференции ISSCC 2022, здесь мы поделимся наиболее важной информацией. После первого поколения память HBM развивалась весьма неспешно вплоть до улучшенной версии второго поколения HBM2E. Конечно, пропускная способность возрастала, но революционного прогресса по емкости и скорости не было.

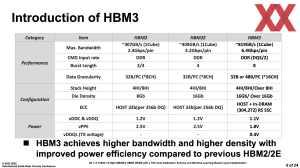

Теперь же можно говорить о существенном прорыве, поскольку пропускная способность на контакт увеличилась до 6,4 Гбит/с, то есть в два раза по сравнению с HBM2. Число каналов удвоилось с восьми до 16. Впрочем, здесь речь идет о двух псевдоканалах на один канал памяти, как и в случае DDR5, когда модуль DDR5 работает по двум виртуальным каналам. Пропускная способность на чип увеличилась до 819 Гбайт/с.

Чтобы увеличить емкость, чипы могут содержать 4, 8, 12 или даже 16 слоев памяти друг над другом, которые соединяются сквозными связями Through-Silicon Via (TSV). Емкость слоев составляет от 8 до 32 Гбит (от 1 до 4 Гбайт). Следовательно, емкость чипов памяти HBM3 может составлять от 4 Гбайт (4-Hi, 4x 1 Гбайт) до 64 Гбайт (16-Hi, 16x 4 Гбайт).

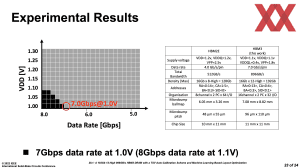

Удалось увеличить и эффективность. В частности, напряжения были снижены с 1,2 до 1,1 В, а также с 2,5 до 1,8 В.

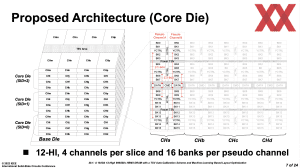

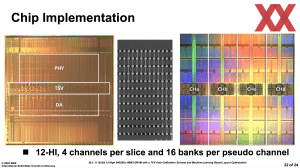

Дизайн HBM3 довольно похож на предыдущие поколения. Имеется подложка Base Die, которую также называют базовым или логическим кристаллом (logic die). На ней расположены ключевые слои Core Die непосредственно с ячейками памяти. Каждый слайс подключен по 4 каналам. Они разделяются на два псевдоканала, в итоге каждый псевдоканал работает с 16 банками памяти.

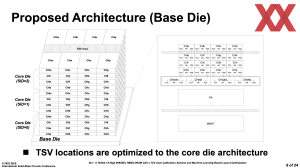

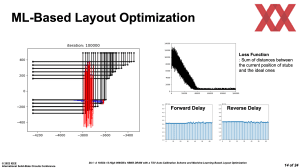

С подожки соединения TSV обеспечивают связь с 12 слоями Core Die, которые позднее будут расширены до 16. Здесь весьма важно расположение TSV в чипе, SK Hynix видит в этом одну из самых серьезных проблем при разработке HBM3. Для наиболее оптимального выбора связей TSV использовался искусственный интеллект. Впрочем, с несколькими тысячами TSV расположить их вручную проблематично, поскольку следует учитывать не только идеальное расположение, но и примерно одинаковую длину. Но в полной мере достичь этого не получится, поэтому без процесса калибровки TSV не обойтись. В результате калибровки гарантируется, что все банки памяти работают как можно с более близкими задержками.

SK также рассказала о новом методе ECC на кристалле HBM3. Здесь компания перешла на код Рида-Соломона для определения и коррекции ошибок. Были пересмотрены блоки кодирования/декодирования, а также коррекции символов (symbol corrector). Чтобы обеспечить возможность коррекции ошибок SK Hynix добавила к 16 символам по 2 символа на ECC и по одному для метаданных, что дало 19 символов в сумме.

Наконец, SK Hynix рассказала о процессе производства. Память HBM3 производится по техпроцессу 1b, размеры корпусировки составляют 11 x 11 мм, то есть они даже чуть больше HBM2E с размером 10 x 11 мм. SJ Hynix будет производить HBM3 в вариантах 12-Hi (24 GB), 8-Hi (16 GB) и 4-Hi (8 GB). Указывается, что в случае памяти HBM3 с 12 уровнями расстояние между ними составляет 30 мкм.

В первых тестах HBM3 пропускная способность памяти составила 7 Гбит/с на контакт, на чип HBM3 - 896 Гбайт/с, причем при напряжении 1,0 В. Но спецификации JEDEC указывают до 1,1 В, и при данном напряжении SK Hynix планирует достичь 8 Гбит/с на контакт.

Пока не совсем понятно, когда именно на рынке появятся чипы HBM3. Пока производители все еще используют HBM2E даже для грядущих ускорителей. Наверняка о начале производства HBM3 будет объявлено уже в этом году, но решения на рынке можно ожидать не раньше 2023.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).