Разработка памяти High Bandwidth Memory за последние годы несколько затормозилась. Производители несколько раз пытались распространить эту память на потребительский сегмент, в частности, AMD (Radeon R9 Fury X, Radeon RX Vega 56 и 64, Radeon VII), но без особого успеха. До сих пор HBM оставался стандартом для дата-центров, хотя NVIDIA выпустила с ним потребительскую видеокарту Titan V.

Разработка памяти High Bandwidth Memory за последние годы несколько затормозилась. Производители несколько раз пытались распространить эту память на потребительский сегмент, в частности, AMD (Radeon R9 Fury X, Radeon RX Vega 56 и 64, Radeon VII), но без особого успеха. До сих пор HBM оставался стандартом для дата-центров, хотя NVIDIA выпустила с ним потребительскую видеокарту Titan V.

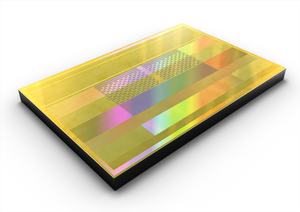

В марте 2019 Samsung рассказала о грядущем варианте HBM2 под названием Flashbolt, который должен работать с пропускной способностью 3,2 Гбит/с. Летом последовала SK Hynix. Теперь стандарт утвержден JEDEC как JESD235C. По техническим спецификациям пропускная способность увеличилась с 2,4 до 3,2 Гбит/с на контакт, что было известно и раньше. Некоторые производители упоминают HBM2 как HBM2E.

Емкость сохранилась на уровне 2 Гбайт на кристалл, до 12 кристаллов могут стыковаться друг над другом. В результате один чип памяти HBM2 может обеспечивать емкость до 24 Гбайт. Впрочем, чипов с подобной максимальной емкостью до сих пор не выпущено. Samsung анонсировала массовое производство на первую половину 2020. Пока неизвестно, кто станет клиентам южнокорейской компании.

Память Samsung Flashbolt изначально не будет соответствовать полным спецификациям HBM2E. Вместо 12 слоев она будет опираться на восемь. Пропускная способность на чип будет ограничена 410 Гбайт/с.

Samsung говорит о перспективе разгона до 4,2 Гбит/с на контакт. Что позволит увеличить пропускную способность памяти до 538 Гбайт/с на чип. Для четырех чипов памяти мы получаем 1,64 Тбайт/с, а с разгоном более 2 Тбайт/с. Конечно, кроме вопроса высокого энергопотребления возникает и проблема контроллера, который должен справляться со столь высокой пропускной способностью.

| HBM2E (JESD235C) | HBM2 (JESD235B) | HBM (JESD235A) | |

| Емкость чипа | 24 GB | 12 GB | 4 / 8 GB |

| Пропускная способность на контакт | 3,2 Гбит/с | 2,4 Гбит/с | 1,6 / 2,0 Гбит/с |

| Слои DRAM | 12 | 12 | 4 / 8 |

| Емкость слоя | 16 Гбит | 8 Гбит | 4 / 8 Гбит |

| Техпроцесс слоев DRAM | 10 нм | 20 нм | 20 нм |

| Интерфейс памяти | 1.024 бит | 1.024 бит | 1.024 бит |

| Пропускная способность на чип | 410 Гбайт/с | 307,2 Гбайт/с | 204,8 Гбайт/с |

| Напряжение | - | 1,2 В | 1,2 В |

Что касается производства, Samsung и SK Hynix, скорее всего, используют техпроцесс класса 10-нм. Подробностей пока нет. Samsung просто называет класс 1y. Следует отметить, что JEDEC не дает каких-либо спецификаций по физическому размеру чипов памяти. Хотя здесь наиболее интересен параметр Z, то есть высота чипов. В прошлом мы наблюдали некоторые упаковки AMD с разной высотой чипов памяти из-за разных производителей. Так что и в случае HBM2E единый стандарт высоты вряд ли будет.

В принципе, основные технические спецификации HBM2E известны уже несколько месяцев. Но официальный стандарт JEDEC и намерение Samsung приступить к массовому производству в первой половине 2020 позволяет спрогнозировать время появления новых продуктов. NVIDIA,скорее всего, представит новую архитектуру для HPC на конференции GTC в конце марта. И она наверняка будет опираться на новую память HBM2.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).