Кроме быстрого интерконнекта важную роль играет максимальная пропускная способность подключенной памяти к GPGPU, ASIC и FPAG. Не все компании готовы разрабатывать контроллеры памяти HBM2E самостоятельно вместе с физическими интерфейсами PHY, и для них Rambus как раз предлагает собственное решение.

Кроме быстрого интерконнекта важную роль играет максимальная пропускная способность подключенной памяти к GPGPU, ASIC и FPAG. Не все компании готовы разрабатывать контроллеры памяти HBM2E самостоятельно вместе с физическими интерфейсами PHY, и для них Rambus как раз предлагает собственное решение.

JEDEC уже опубликовала спецификации HBM2E на скорости 3,2 Гбит/с, компании SK Hynix и Samsung объявили скорое массовое производство чипов памяти. TSMC, вместе с Broadcom, тоже объявила о разработке памяти HBM2E. Как полагают многие эксперты, NVIDIA и AMD одними из первых перейду на новую память HBM2E.

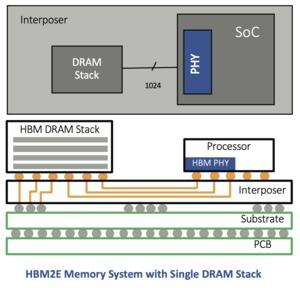

Решение, представленное Rambus, подключает память HBM2E по 1.024-битному интерфейсу с пропускной способностью 3,2 Гбит/с на контакт. Поддерживаются стеки памяти до 12 слоев.

Контроллер памяти поддерживает восемь каналов и 16 псевдо-каналов. Хотя Rambus предлагает контроллер и PHY, вполне возможно использовать только контроллер Rambus и проприетарное решение PHY (PHY Independent Mode). В так называемой ориентации восток-запад PHY может располагаться располагается по углам чипа.

Rambus предлагает заинтересованным в HBM2E компаниям полную поддержку по интеграции технологии. В том числе программную поддержку для контроллера памяти.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).