За последние дни появилось довольно много информации о грядущих материнских платах X570, которые будут анонсированы на Computex. Вместе с тем утек слайд закрытой презентации, на котором показана диаграмма соединения процессора Ryzen с чипсетом и другими компонентами.

За последние дни появилось довольно много информации о грядущих материнских платах X570, которые будут анонсированы на Computex. Вместе с тем утек слайд закрытой презентации, на котором показана диаграмма соединения процессора Ryzen с чипсетом и другими компонентами.

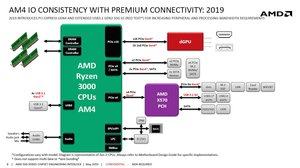

Самой большой инновацией процессоров Ryzen третьего поколения можно назвать дизайн chiplet. Кристалл ввода/вывода обеспечивает внутренние и внешние соединения передачи данных, один или два кристалла CPU (в зависимости от модели) содержит вычислительные ядра на основе архитектуры Zen 2. Впрочем, на диаграмме показана только упаковка в целом. Приведенные соединения, скорее всего, осуществляются через кристалл ввода/вывода.

С технической точки зрения стоит отметить, что все процессоры AMD на архитектуре Zen 2 будут поддерживать PCI Express 4.0. На диаграмме показано распределение линий и интерфейсов. Число линий остается идентичным двум первым поколениям Ryzen: 1x 16 + 1x 4 плюс еще четыре для подключения чипсета.

Как и ожидалось, видеокарта подключается по 16 линиям. Возможно разделение на два подключения по восемь линий. Четыре линии доступны для устройств NVMe и SATA, которые тоже могут разделяться, в зависимости от используемого аппаратного обеспечения. Четыре линии PCI Express используются для соединения процессора Ryzen и чипсета.

Чипсет, с другой стороны, обеспечивает дополнительные подключения, которые затем проходят по четырем линиям PCI между CPU и чипсетом. На диаграмме видны дополнительные устройства PCI Express 4.0, подключенные к чипсету. Также есть интерфейс USB 3.1 Gen 2 и SATA. К сожалению, диаграмма не дает представление об их количестве.

Кроме линий PCI Express, к процессору Ryzen подключены четыре порта USB 3.1 Gen 2. Также отметим двухканальный интерфейс памяти и протоколы SPI, LPC и SMBus, обеспечивающие в том числе связь процессора и BIOS.

Презентация датирована маем 2019 года и отражает эталонный сценарий. В зависимости от материнской платы, линии и разъемы могут быть распределены иначе. На Computex мы наверняка увидим разные реализации того, что представлено в схематическом виде на диаграмме выше.