На производительность современных процессоров, графических ускорителей и SoC в целом довольно существенно влияют межсоединения, обеспечивающие передачу данных. Здесь можно упомянуть такие разработки, как Intel Omni-Path или NVIDIA NVLink, представляющие собой альтернативы PCI Express. Кроме того, и соединения внутри SoC тоже представляют собой фундаментальную проблему.

На производительность современных процессоров, графических ускорителей и SoC в целом довольно существенно влияют межсоединения, обеспечивающие передачу данных. Здесь можно упомянуть такие разработки, как Intel Omni-Path или NVIDIA NVLink, представляющие собой альтернативы PCI Express. Кроме того, и соединения внутри SoC тоже представляют собой фундаментальную проблему.

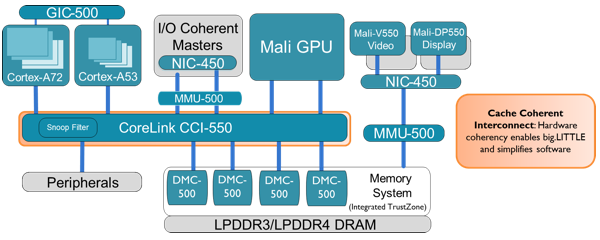

ARM представила CoreLink CCI-550 или Cache Coherent Interconnect. Благодаря CoreLink CCI-550 ARM планирует добиться когерентности кэша между кластером CPU LITTLE.big, графическим процессором Mali и другими компонентами SoC. Здесь неизбежно поднимается тема гетерогенных вычислений, которую мы недавно обсудили в статье, посвященной технологии AMD HSA. Суть заключается в том, чтобы обеспечить обмен данными и единую базу данных для обработки на разных вычислительных устройствах. Все это призвано упростить программирование и увеличить производительность выполнения задач. CoreLink CCI-550 – вполне логичное расширение усилий в рамках направления Cache Coherent Interconnect от ARM.

CoreLink CCI-550 позволяет соединить до шести интерфейсов ACE (кластер LITTLE.big, Mali GPU и другие компоненты). Пропускная способность составляет до 50 Гбайт/с, так что интерконнект ARM хорошо ориентирован на будущие требования систем. Теперь подобные системы могут справляться даже со сложными многозадачными сценариями. Дисплеи 4K, как внутренние, так и внешние тоже без проблем будут поддерживаться планшетами и смартфонами будущего. Конечно, ARM фокусируется на взаимодействии собственной архитектуры LITTLE.big и Mali GPU, в качестве примеров, выигрывающих от Cache Coherent Interconnect, называются стабилизация изображения высокого разрешения в реальном времени, выполнение сложного контент-ориентированного поиска, а также приложения гетерогенных вычислений.

Впрочем, до выдачи первых лицензий ARM на CoreLink CCI-550 Cache Coherent Interconnect пройдет еще несколько месяцев. И до конца 2016 года вряд ли стоит ожидать появление продуктов на рынке.

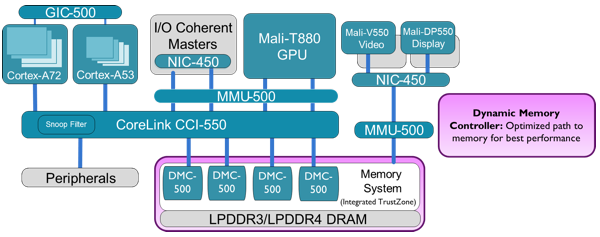

CoreLink DMC-500 Dynamic Memory Controller

Здесь стоит упомянуть и новый CoreLink DMC-500 Dynamic Memory Controller. Он призван обеспечивать быстрый обмен данных с оперативной памятью. К концу следующего года должны появиться SoC с поддержкой частоты памтяи LPDDR3-2133 и LPDDR4-4267. Контроллер является составной частью SoC, каждый работает со своим каналом. ARM указывает на использование до четырех контроллеров памяти в дизайнах SoC, что дает 4-канальную систему. С CoreLink DMC-500 Dynamic Memory Controller ARM планирует увеличить пропускную способность на 27% и уменьшить задержки на 65% по сравнению с предшественником Core Link DMC-400).