Несмотря на все негативные прогнозы, серверные процессоры и CPU для дата-центров на основе ядер ARM продолжают развиваться. Хотя их рынок не такой большой, мнения экспертов склоняются к тому, что в будущем мы получим еще больше подобных решений. Сильной стороной подобных процессоров является масштабируемость под нужные задачи, и многие производители уже представили многоядерные модели: Ampere eMag (32 ядра), Cavium ThunderX2 (32 ядра) и Qualcomm Centriq 2400 (48 ядер). Huawei Kunpeng 920 опирается на 64 ядра ARM и производится по 7-нм техпроцессу.

Несмотря на все негативные прогнозы, серверные процессоры и CPU для дата-центров на основе ядер ARM продолжают развиваться. Хотя их рынок не такой большой, мнения экспертов склоняются к тому, что в будущем мы получим еще больше подобных решений. Сильной стороной подобных процессоров является масштабируемость под нужные задачи, и многие производители уже представили многоядерные модели: Ampere eMag (32 ядра), Cavium ThunderX2 (32 ядра) и Qualcomm Centriq 2400 (48 ядер). Huawei Kunpeng 920 опирается на 64 ядра ARM и производится по 7-нм техпроцессу.

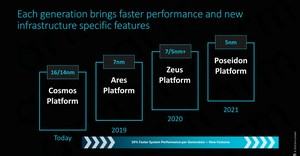

С 2019 года сама ARM меняет подход, на что указывают Neoverse N1 и E1. Соответствующая платформа названа "Ares", чипы будут производиться по 7-нм техпроцессу. В 2020 году можно ожидать платформу "Zeus" и производство по технологиям 7 и 5 нм. К 2021 году платформа "Poseidon" полностью перейдет на 5 нм. Так что планы у ARM наполеоновские.

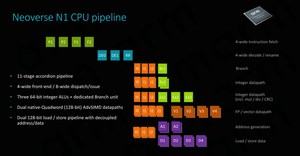

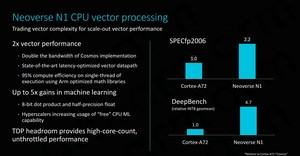

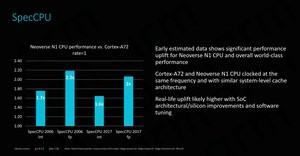

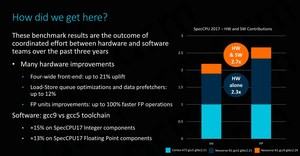

Основой ядер CPU N1 является такой же конвейер, что и у дизайна Cortex-A76. Блок выборки (fetch) имеет ширину 4 команды, передняя часть конвейера насчитывает 11 ступеней. В задней части конвейера расположены три АЛУ - два простых и один с возможностью сложных умножений и делений, а также два 128-битных конвейера SIMD для вычислений с плавающей запятой и векторных расчетов.

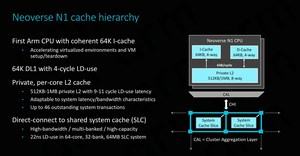

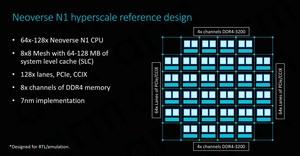

Что касается кэшей, ARM установила по 64 кбайт кэша инструкций и данных L1, а также 512 или 1.204 кбайт кэш L2. Также имеется 128 Мбайт кэша System Level Cache (SLC), доступного для всех ядер. Цель заключается в том, чтобы минимизировать задержки всей системы кэширования. Буферы предсказания ветвлений сделаны очень большими, чтобы минимизировать промахи ветвлений.

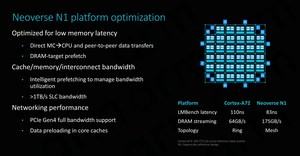

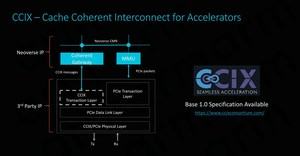

Основой SoC на ядрах N1 является Component Aggregation Layer (CAL). Он предназначен для работы в ячеистой топологии и содержит два интерфейса. Первый интерфейс обращен к сетевому уровню, состоящему из многочисленных пересечений XP (Crosspoint) ячеистой сети, которые представляют собой коммутаторы или роутеры. Второй интерфейс CAL обращен к кэшу System Level Cache. Mesh-сеть работает на 2/3 частоты ядер CPU и оптимизирована под минимальные задержки. Пропускная способность по сравнению с дизайном Cortex A72 была увеличена более чем в два раза.

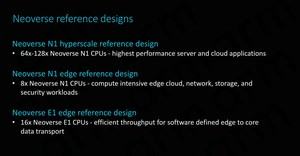

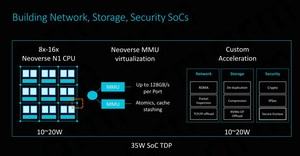

ARM на основе N1 CPU предлагает различные эталонные платформы. Дизайн N1 Edge ориентирован на сетевые и облачные решения, системы хранения данных. Здесь ARM использует до восьми ядер Neoverse N1. Дизайн N1 Hyperscale призван показать полный потенциал архитектуры. Здесь используются уже от 64 до 128 ядер N1 в ячеистой топологии 8x8. Объем System Level Cache составляет 64 или 128 Мбайт. Также доступны 128 линий PCI Express 4.0 и 8-канальный интерфейс памяти.

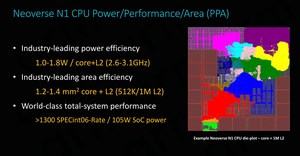

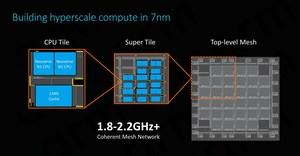

Подобная SoC: блоки "CPU tiles" или плитки состоят из двух ядер N1 каждый. Восемь подобных плиток формируют "Super Tile". В итоге мы получаем строительные блоки дизайна N1 Hyperscale, в котором может насчитываться до 128 ядер. Mesh-сеть будет работать на частотах между 1,8 и 2,2 ГГц. Если данный уровень составляет 2/3 от частоты ядер, то в случае последних мы получим от 2,4 до 3,0 ГГц.

Подобная SoC будет потреблять 105 Вт (в варианте с 64 ядрами). Впрочем, в зависимости от сценария, она может значительно обгонять процессоры Intel и AMD с 28 и 32 ядрами по производительности, так что эффективность должна быть выше.

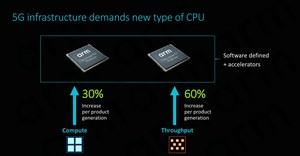

Neoverse E1 - первый дизайн ARM с поддержкой SMT

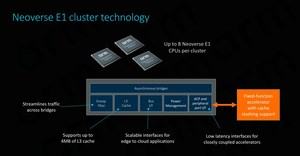

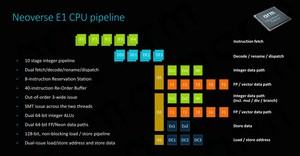

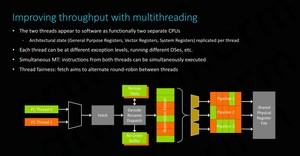

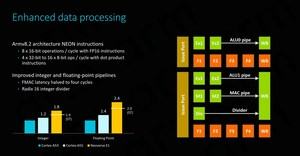

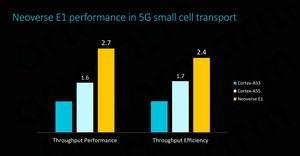

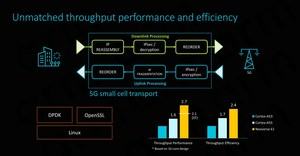

Дизайн Neoverse N1 ориентирован на максимальную производительность, в случае Neoverse E1 ARM поставила в приоритет обработку больших массивов данных. Мы получаем первый серверный процессор ARM с поддержкой SMT (Simultaneous Multi Threading).

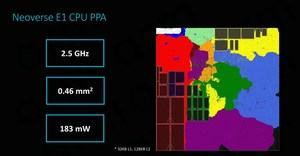

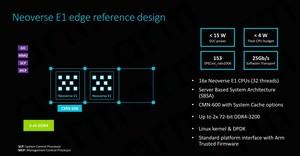

Система кэшей и блоков выборки была изменена с учетом выполнения нескольких потоков одновременно. Дизайн Neoverse E1 предусматривает до 16 ядер на SoC. Теоретически возможно и больше, но многие компоненты и кэш System Level Cache ориентированы на работу с кластером 2x 8 ядер. Подобный процессор работает с памятью DDR4-3200 по двухканальному интерфейсу. Энергопотребление всей SoC должно составлять меньше 15 Вт, причем самим ядрам требуется только 4 Вт - что еще раз показывает, что значительный вклад в бюджет энергопотребления вносят другие компоненты, подобные сетевым интерфейсам.

ARM ставит амбициозные цели

Анонс Neoverse E1 и Neoverse N1 показывает весьма серьезные амбиции ARM по завоеванию серверного рынка. ARM не собирается довольствоваться нишевым сегментом, компания планирует конкурировать с Intel и AMD. Та же Huawei за последние месяцы наглядно показала, что разработка собственных серверных процессоров на дизайне ARM является весьма перспективным направлением. ARM преобразовала дизайны Cortex в специализированные серверные платформы Neoverse E1 и Neoverse N1.

В следующие два года нас ждет интересная битва концепций. ARM ожидает, что первая коммерческая реализация платформы Neoverse N1 появится не ранее чем через 12 месяцев. Серверный рынок довольно инерционный, и на замену платформ может уйти несколько лет.