Кроме новых процессоров Xeon (Xeon D-1600 и Xeon Scalable второго поколения) Intel представила аппаратные новинки и в других сферах. Уже несколько лет Intel работает над чипами Falcon Mesa в дизайне FPGA, которые хорошо вписываются в текущую стратегию чипового гиганта.

Уже давно стало понятно, что Intel планирует опереться на более гибкие подходы в будущем. Начнем с техпроцесса, раньше он был привязан к конкретным продуктам. Но если с техпроцессом возникнут непредвиденные проблемы, как совсем недавно произошло с 10-нм техпроцессом, связанные с ним продукты выпустить не получится. Intel как раз собирается решить данную проблему, что видно по линейкам продуктов.

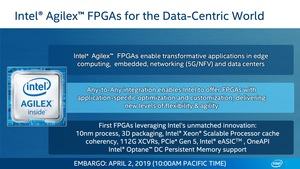

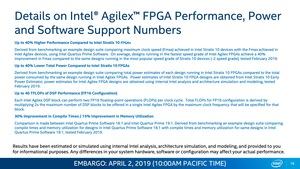

Одна из линеек - чипы FPGAs, которые выйдут на рынок в виде Agilex в третьем квартале. Кристаллы будут производиться по 10-нм техпроцессу, но дизайн chiplet позволяет использовать и другие техпроцессы. В данном случае важно соединение с процессором Xeon с сохранением когерентности кэша. Подобная связка должна быть весьма эффективна в определенных сценариях. В целом, Intel сможет использовать дизайн chiplet для объединения чипов разных типов, что позволит предложить гибкие решения, оптимизированные под целевые сценарии.

Покупка компании eASIC в середине прошлого года оказалась значимым шагом на пути Intel. Компания 19 лет разрабатывала ASICs и FPGAs для своих клиентов. Причем она занималась всеми этапами, от первых идей до поставки чипов. Подобная компетенция теперь перешла под "зонтик" Intel. Напомним, что среди всего прочего чиповый гигант владеет технологией EMIB (Embedded Multi-die Interconnect Bridge), позволяющей соединять FPGAs и классические вычислительные кристаллы. Что уже происходит сегодня, но в будущем наверняка станет играть еще более важную роль. Для чипов Agilex, опять же.

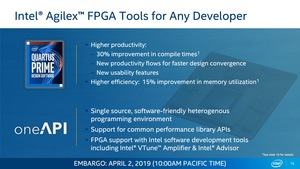

Представленный на слайде дизайн, который скрывается под чипами Agilex, уже знаком нам под кодовым названием Falcon Mesa. Для создания подобного чипа потребовалась доработка некоторых технологий, в том числе второго поколения Hyperflex. Чип выходит в третьем квартале 2019, поэтому поддержка DDR5 и PCI Express 5.0 явно ориентирована на будущее.

Intel подчеркивает гибкость чипов Agilex, которые можно изменять, в зависимости от целевых сценариев. Например, добавлять контроллеры HBM2, линии PCI Express или трансиверы 112G.

Для соединения отдельных кристаллов используется технология Embedded Multi-The Interconnect Bridge (EMIB). Она позволяет располагать на подложке разные ядра. Подобный дизайн 2.5D может использоваться для связи разных типов кристаллов, соединение обеспечивается сквозными каналами TSV (Through Silicon Vias). В отличие от других технологий подложек, EMIB не использует крупный дополнительный кристалл для подключения всех контактных точек. И площадь поверхности, на которой располагаются контакты TSV, сравнительно невелика.

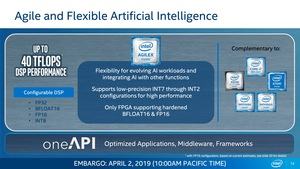

Один из наиболее важных сценариев использования чипов Agilex - инференс, то есть обработка запросов в сеть глубокого обучения. Инференс заключается в отправке в тренированную сеть глубокого обучения данных с сенсоров, после чего результат должен быть получен как можно быстрее. FPGAs могут содержать конфигурируемые ЦСП/DSP для обработки FP32, BFloat16, FP16 или INT8. Также могут обрабатываться и менее точные форматы данных, хотя на практике они распространены не так широко. Здесь сначала предстоит провести исследовательскую работу. В любом случае, поддержка форматов от INT7 до INT2 тоже планируется, хотя она и не станет уникальной функцией Agilex. Та же NVIDIA поддерживает эти форматы в ядрах Tensor.

Но чипы Agilex пока будут единственными с аппаратной поддержкой форматов FP16 и Bfloat16. С процессорами Cooper Lake Xeon формат Bfloat16 тоже будет штатно поддерживаться.

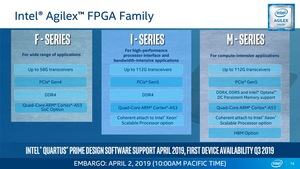

В третьем квартале выйдут три серии:

- F-Series: трансивер 58G, PCI Express 4.0, контроллер DDR4, Quad Core ARM (Cortex-A53) в качестве

- I-Series: трансивер 112G, PCI Express 5.0, контроллер DDR4, Quad Core ARM (Cortex-A53), когерентное подключение к процессорам Xeon

- M-Series: трансивер 112G, PCI Express 5.0, контроллер DDR5, Optane DC Persistent Memory, Quad-Core ARM (Cortex-A53), когерентное подключение к процессорам Xeon, опция контроллера HBM

С чипами Agilex Intel позиционирует себя на рынок, который частично охвачен процессорами Xeon-D, но который благодаря гибкости FPGAs получится завоевать намного шире. В качестве потенциальных сценариев можно отметить сетевые решения, дата центры и т.д.

По мере приближения третьего квартала мы наверняка получим более подробную информацию о конкретных моделях FPGAs. Весьма удивляет то, что Intel уже начала говорить о поддержке DDR5 и PCI Express 5.0, поскольку данные стандарты пока не финализированы.