Intel раскрыла новые подробности нейропроцессора Nervana Neural Network Processor for Training (NNP-T), о чем сообщили наши коллеги Tomshardware. Появились новые интересные детали. Например, NNP-T опирается на 27 млрд. транзисторов и 32 Гбайт памяти HBM2, кристаллы установлены на подложку площадью 1.200 мм².

Intel раскрыла новые подробности нейропроцессора Nervana Neural Network Processor for Training (NNP-T), о чем сообщили наши коллеги Tomshardware. Появились новые интересные детали. Например, NNP-T опирается на 27 млрд. транзисторов и 32 Гбайт памяти HBM2, кристаллы установлены на подложку площадью 1.200 мм².

NNP-T является антиподом NNP-I - последний предназначен для инференса, а NNP-T берет на себя задачи тренировки сетей глубокого обучения. Помимо прочего, NNP-I использует ядра Sunny Cove и инструкции AVX512 для ускорения вычислений.

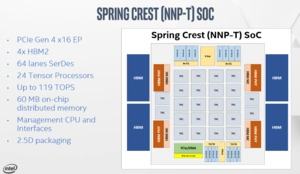

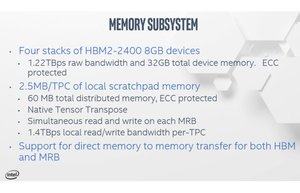

Но перейдем к структуре NNP-T. Чип состоит из 24 тензорных процессоров (Tensor Processors, TPCs). Они обеспечивают вычислительную производительность 119 TOPS. SoC оснащена 60 Мбайт встроенной памяти (SRAM). Чтобы оперативная память была как можно ближе к TPCs, Intel установила четыре чипа HBM2 емкостью 8 Гбайт каждый, что дает 32 Гбайт. Также имеется интерфейс PCIe 4.0 с 16 линиями, 64 линии SerDes для памяти HBM2. SoC и четыре чипа HBM2 установлены на подложку площадью 1.200 мм².

Чип NNP-T производится TSMC по 16-нм техпроцессу (CLN16FF +). Недавно TSMC показала упаковку с двумя крупными кристаллами и несколькими чипами HBM2, установленными на подложку площадью 2.500 mm². NNP-T тоже опирается на упаковку Chip-on-Wafer-on-Substrate (CoWoS). Честно говоря, было довольно странно слышать о том, что Intel во время презентации сообщает о производстве чипа на мощностях TSMC.

Упаковка NNP-T размером 60 x 60 мм содержит 3.325 контакта BGA. Таким образом, NNP-T устанавливается не в сокет, а припаивается к материнской плате. Чип NNP-T работает на тактовой частоте 1,1 ГГц, TDP можно будет настраивать от 150 до 250 Вт.

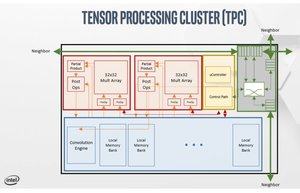

Отдельные TPC должны как можно быстрее получать данные для обработки. Поэтому каждый TPC имеет четыре скоростных подключения, два предназначены для работы с памятью HBM2, а оставшиеся два - для полносвязного интерконнекта (2D Mesh). Блоки TCP поддерживают формат bFloat16 для матричных умножений, FP32 и FP16.

Одиночные NNP-T будут использоваться в редких случаях, поскольку Intel нацеливается на крупные серверы, содержащие 1.024 узла. Каждый узел состоит из восьми ускорителей NNP-T. Впрочем, пока Intel тестировала серверы только до 256 ускорителей, то же самое касается нынешних возможностей масштабирования программного обеспечения. Но в ближайшие месяцы Intel улучшит масштабирование и перейдет на большее количество NNP-T.

Если верить Intel, опытные образцы NNP-T уже производятся, они будут разосланы ключевым партнерам уже в этом году. В 2020 ожидается широкая доступность ускорителей. На данный момент Intel выпускает кристаллы в B-степпинге, который соответствует финальному дизайну.