Еще осенью 2019 года TSMC объявила о готовности старта массового производства по 5-нм техпроцессу. Первые чипы должны выйти с конвейера этим летом, на данный момент они проходят стадию тестирования. Наши коллеги WikiChip скомпилировали имеющуюся информацию по 5-нм техпроцессу, в том числе с конференций Techcon 2019, IEEE IEDM и ISSCC 2020.

Еще осенью 2019 года TSMC объявила о готовности старта массового производства по 5-нм техпроцессу. Первые чипы должны выйти с конвейера этим летом, на данный момент они проходят стадию тестирования. Наши коллеги WikiChip скомпилировали имеющуюся информацию по 5-нм техпроцессу, в том числе с конференций Techcon 2019, IEEE IEDM и ISSCC 2020.

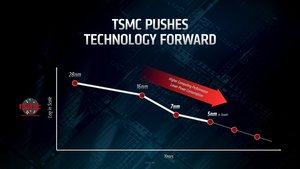

TSMC довольно существенно продвинулась вперед и по предыдущим техпроцессам. Хорошим примером можно назвать техпроцесс 7 нм, производственные мощности которого сегодня полностью загружены. Схожую картину мы наверняка получим и с техпроцессом 5 нм, поскольку та же Apple, будучи одним из крупнейших клиентов, выкупила значительные мощности. Напомним, что TSMC запустила массовое производство 7-нм чипов лишь два года назад.

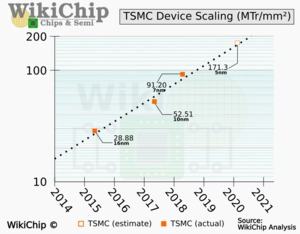

Конечно, разные техпроцессы довольно сложно сравнивать между собой. Одним из хороших критериев можно назвать число транзисторов на квадратный миллиметр. И по нему можно сравнивать техпроцессы разных производителей. Например, TSMC упаковывает 28,88 миллионов транзисторов на квадратный миллиметр (MTr/mm²) по техпроцессу 16 нм, 52,51 MTr/mm² по техпроцессу 10 нм и 91,2 MTr/mm² по техпроцессу 7 нм. Сама TSMC говорит о том, что транзисторы при переходе на 5-нм техпроцесс удается упаковывать плотнее в 1,84 раза. Что означает 167,8 MTr/mm². Если верить аналитике WikiChip, TSMC сможет достичь плотности упаковки 171,3 MTr/mm². Что указывает на практически линейный рост.

Конечно, весьма интересно сравнение с Intel. В случае 14nm++ техпроцесса Intel достигла плотности 37,22 MTr/mm², а техпроцесс 10 нм дает около 100 MTr/mm². Samsung перешла на техпроцесс 7 нм с плотностью от 85 до 95 MTr/mm². Впрочем, плотность упаковки зависит от того, ориентирован чип на максимальную производительность или минимальное энергопотребление.

EUV экономит слои

Процесс изготовления чипов многоступенчатый, слои экспонируются один за другим. Текущий техпроцесс TSMC опирается на литографию с глубоким ультрафиолетом DUV (Deep Ultra Violet) для большинства металлическим слоев. В случае техпроцесса N7+ технология экстремально глубокого ультрафиолета EUV используется лишь для нескольких слоев. Но на техпроцессе 5 нм (N5) планируется полностью перейти на EUV. Техпроцесс EUV позволяет сэкономить на слоях металла и масках, несмотря на более сложную экспозицию. Однако можно будет обойтись без дополнительных слоев с металлическими соединениями.

Изготавливать множество масок тоже не потребуется. Intel недавно на видеоролике рассказала о том, как используются маски. Они переносят паттерны на светочувствительный материал во время экспозиции. После чего с помощью травления создаются транзисторы и логические цепи.

Без EUV 5-нм техпроцесс потребовал бы 115 масок. Благодаря переходу на EUV число масок удалось сократить до 80. Техпроцесс DUV 7 нм требует использования 87 масок. Разработка и производство масок - процесс очень затратный. Поэтому чем больше масок требуется, тем сложнее и дороже получается весь техпроцесс.

TSMC ожидает, что старт 5-нм техпроцесса будет более динамичным и быстрым, чем в случае 7 нм. Хотя и 7-нм техпроцесс TSMC запустила очень удачно. Тестовое производство было начато год назад, так что TSMC готовится поставить новые рекорды. С новым техпроцессом 5 нм TSMC выйдет в лидеры среди контрактных производителей. Samsung чуть позднее запустит свой 5-нм техпроцесс, однако корейская компания планирует революцию со своим 3-нм техпроцессом. Что касается 7-нм техпроцесса Intel, то здесь подробностей пока нет. Первые 7-нм GPU должны выйти с конвейера Intel до наступления 2021 года.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).