На конференции Technology Symposium TSMC в виртуальной форме рассказала о прогрессе, достигнутом в сфере производства полупроводников. TSMC планирует в этом году увеличить объемы 5-нм производства, а к 2022 году перейти на 3 нм.

На конференции Technology Symposium TSMC в виртуальной форме рассказала о прогрессе, достигнутом в сфере производства полупроводников. TSMC планирует в этом году увеличить объемы 5-нм производства, а к 2022 году перейти на 3 нм.

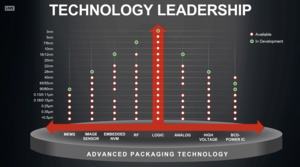

TSMC сообщает об улучшениях почти по всем техпроцессам. Например, TSMC предлагает оптимизированный 12-нм техпроцесс (N12e), который заменит нынешнее производство 22ULL (22 нм, ultra low voltage). N12e базируется на ранее внедренном 12FFC+_ULL, но предлагает дополнительные оптимизации. С техпроцессом N12e TSMC ориентируется на компоненты IoT и Edge, которые должны работать наиболее эффективно.

По сравнению с 22ULL, техпроцесс N12e позволит сделать чипы на 49% быстрее при прежнем энергопотреблении. Плотность упаковки транзисторов увеличилась на 76%. Чипы, выпускаемые по техпроцессу N12e, на 55% более экономичны при прежнем уровне производительности. Поскольку в подобных чипах используется все больше памяти SRAM, плотность упаковки транзисторов очень важна. Токи утечки SRAM были снижены на 50%, что снижает энергопотребление. Чипы по техпроцессу N12e могут работать от напряжений 0,4 В, поэтому их можно назвать очень экономичными.

N5 и N3 - основные драйверы роста для TSMC

TSMC предлагает и другие техпроцессы помимо упомянутых. Конечно, основным для TSMC сегодня является 7-нм техпроцесс. Техпроцесс N7/N7P на данный момент используют такие крупные клиенты, как AMD, NVIDIA и Apple. Конечно, более интересно следующее поколение N5. В частности, чипы Apple A-Series SoC нового поколения будут производиться по N5, как и первые чипы Apple Silicon в рамках инициативы по переоснащению Mac собственными процессорами. Со второго квартала 2020 TSMC уже начала массовое производство чипов по 5-нм техпроцессу.

Следующим шагом станет техпроцесс N5P, доступ к которому получат сначала ограниченное число партнеров TSMC. По сравнению с N5, техпроцесс N5P должен снизить энергопотребление на 10%. Производительность при этом увеличится на 5%. Первые чипы N5P сойдут с конвейера TSMC в 2021 году. 5-нм чипы буду производиться на заводе Fab18 в Южной Корее. TSMC на своем четвертом заводе наняла порядка 9.000 сотрудников.

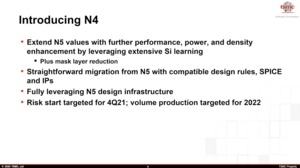

Следующий этап - техпроцесс N4. TSMC планирует с 4-нм техпроцессом использовать больше слоев EUV, чем с N5/N5P. Причем переход на N4 должен быть возможен без существенного изменения дизайнов по сравнению с N5/N5P. Что обеспечит наиболее простую миграцию для клиентов TSMC. По улучшению энергопотребления и производительности показателей пока не представлено.

Пробное производство N4 начнется в четвертом квартале 2021. Массовое производство запланировано на 2022.

| Энергопотребление | Производительность | Плотность упаковки | |

| N10 на N7 | - 40 % | - | x 1.4 |

| N7 на N5 | -30 % | +15 % | x 1,8 |

| N5 на N5P | -10 % | + 5 % | - |

| N5 на N3 | -25 - 30 % | +10 - 15 % | x 1,7 |

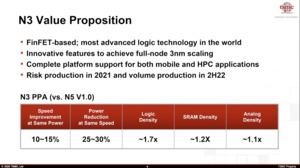

Крупным шагом для TSMC станет 3-нм техпроцесс N3. В отличие от Samsung (Multi Bridge Channel FET), TSMC с техпроцессом 3 нм не будет переходить на новую технологию транзисторов, предпочитая старую добрую FinFET. По сравнению с N5, техпроцесс N3 позволит увеличить производительность чипов на 10-15%. Энергопотребление планируется снизить на 25-30%.

Плотность упаковки транзисторов должна увеличиться в 1,7 раза. Впрочем, здесь TSMC придется столкнуться с рядом ограничений. Компоненты SRAM в случае N3 можно будет уменьшить лишь на 20%. Аналоговые компоненты - лишь на 10%.

Опытное производство N3 намечено на 2021 год. Массовое производство чипов N3 - на вторую половину 2022.

Конференция TSMC Technology Symposium проходит сегодня, а также завтра. Еще один интересный вопрос касается технологий корпусировки. И TSMC наверняка расскажет о своих инновациях в данной сфере.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

Мы рекомендуем ознакомиться с нашим руководством по выбору лучшего процессора Intel и AMD на текущий квартал. Оно поможет выбрать оптимальный CPU за свои деньги и не запутаться в ассортименте моделей на рынке.