На нынешней конференции IEEE International Electron Devices Meeting (IEDM) Intel представила различные разработки в сфере производства полупроводников. И одна из них описывает транзисторы Self-Aligned 3D Stacked Multi-Ribbon CMOS - то есть упорядоченный стек транзисторов с нанолентами. По сути, Intel может теоретически удвоить плотность расположения транзисторов.

На нынешней конференции IEEE International Electron Devices Meeting (IEDM) Intel представила различные разработки в сфере производства полупроводников. И одна из них описывает транзисторы Self-Aligned 3D Stacked Multi-Ribbon CMOS - то есть упорядоченный стек транзисторов с нанолентами. По сути, Intel может теоретически удвоить плотность расположения транзисторов.

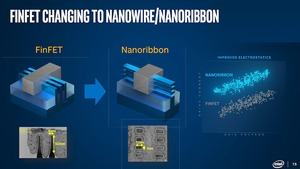

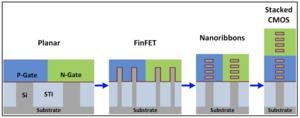

Хотя транзисторы современных полупроводниковых чипов уже представляют собой 3D-транзисторы FinFET, расположение на кристалле все равно планарное, то есть по соседству друг с другом. Подобно Samsung и TSMC, Intel работает над новыми типами транзисторов с нанолентами или нанопроводами в виде Gate All Around (GAA). В транзисторах GAA затвор окружает очень тонкий проводящий канал со всех четырех сторон. Подобный подход позволяет преодолеть ограничения физического масштабирования и энергопотребления FinFET, уменьшив напряжение работы транзисторов. Что повышает их производительность.

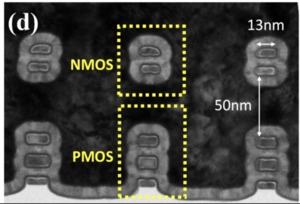

В будущем Intel планирует перейти на упомянутые транзисторы Self-Aligned 3D Stacked Multi-Ribbon CMOS, что позволит уменьшить площадь, занимаемую транзистором. Два транзистора располагаются в стеке, то есть друг над другом, при этом производятся они на одном этапе конвейера (то есть здесь нет, например, раздельного производства и затем склеивания). Конечно, для этого требуется внести изменения в процесс производства транзисторов с нанолентами.

Как видим, две верхних наноленты работают в верхнем транзисторе типа NMOS. Нижний транзистор типа PMOS может состоять из различного числа нанолент, что приводит к изменению рабочего напряжения транзистора и проходимого тока.

Intel указывает, что производство данных транзисторов не создаст серьезных проблем, поскольку техпроцесс все равно придется отрабатывать с нанолентами. Но с двумя транзисторами Intel придется вносить дальнейшие оптимизации, поскольку производительность двух транзисторов в стеке вряд ли будет соответствовать двум обычным транзисторам.

Пройдет несколько лет, прежде чем Intel сможет перейти к массовому производству транзисторов с нанолистами/нанолентами, а также типа GAA в целом. Недавно Intel называла срок в пять лет. Samsung и TSMC тоже работают над подобными технологиями. Но транзисторы Self-Aligned 3D Stacked Multi-Ribbon CMOS открывают новые возможности, в том числе по плотности расположения транзисторов. Сегодня чипы состоят из транзисторов разного типа. Что будет верно и в будущем. Транзисторы GAA обещают существенный прирост производительности по сравнению с нынешними FinFET. Транзисторы Self-Aligned 3D Stacked увеличат плотность упаковки, например, для кэша и SRAM. Можно ожидать, что будущие процессоры Intel продолжат использовать разные типы транзисторов.

Другие инновации на IEDM от Intel

Также Intel показала первые транзисторы High-Performance Short-Channel Gate-All-Around, производство с интеграцией GaN NMOS/Si CMOS на 300-мм подложке, встроенную систему On-Die Metall Interconnect со специальной геометрией, что должно улучить производительность интерконнектов.

Также были показаны суб-ТГц устройства на органической подложке, которую планируется использовать для будущих продуктов.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).