Intel вчера вечером провела стрим "Intel Accelerated", в рамках которого поделилась своими планами в сфере техпроцессов и технологий корпусировки. CEO Intel Патрик Гелсингер и доктор Энн Келлехер, старший вице-президент и генеральный менеджер Intel по развитию технологий, вновь подчеркнули фундаментальные принципы стратегии IDM 2.0. Суть в том, что Intel продолжит использовать внешнее производство на мощностях TSMC, Samsung и GlobalFoundies (возможно, даже нарастит его). Но Intel в будущем планирует вернуть себе роль лидера полупроводникового производства, причем как для собственных продуктов, так и для предоставления своих мощностей для производства чипов сторонним компаниям.

Intel вчера вечером провела стрим "Intel Accelerated", в рамках которого поделилась своими планами в сфере техпроцессов и технологий корпусировки. CEO Intel Патрик Гелсингер и доктор Энн Келлехер, старший вице-президент и генеральный менеджер Intel по развитию технологий, вновь подчеркнули фундаментальные принципы стратегии IDM 2.0. Суть в том, что Intel продолжит использовать внешнее производство на мощностях TSMC, Samsung и GlobalFoundies (возможно, даже нарастит его). Но Intel в будущем планирует вернуть себе роль лидера полупроводникового производства, причем как для собственных продуктов, так и для предоставления своих мощностей для производства чипов сторонним компаниям.

Техпроцессы 14nm, 14nm+, 14nm++, 14nm+++, вечные проблемы с 10-нм производством, неудачный техпроцесс 10nm+ - все эти вехи оказались печальным опытом для Intel, как и отсутствие должной коммуникации с обществом. Наконец, с техпроцессом 10nm SuperFin удалось решить часть проблем. Конечно, все это нисколько не радует, Intel потребовалось очень много времени, чтобы выпустить функционирующие продукты. Вероятно, Intel тщетно пыталась обойтись без дорогих этапов EUV на большей части конвейера, что и стало основной причиной неудач помимо прочего. Только процессоры Tiger Lake достигли ожидаемого уровня производительности и выхода годных кристаллов по техпроцессу 10nm SuperFin. Но в случае настольных ПК данное спасение появилось слишком поздно, вплоть до нынешнего поколения Rocket Lake Intel продолжает использовать 14-нм техпроцесс, хотя CPU Xeon уже производятся по 10-нм техпроцессу (10nm SuperFin) с поколения Ice Lake-SP.

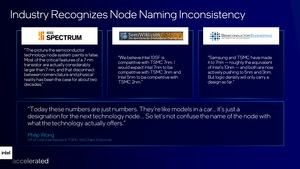

С техпроцессом Enhanced 10nm SuperFin Intel сделала следующий шаг, причем он станет последним с нынешней схемой именования. В принципе, спецификации в нанометрах уже давно превратились в инструмент маркетинга, они имеют малого общего с реальным размером структур на кристалле. По этой причине многие производители указывают рекордно низкие нанометры. Например, 7-нм техпроцесс TSMC и Samsung по плотности расположения транзисторов идентичен 10-нм Intel. Все же спецификации разных производителей полупроводников нельзя сравнивать напрямую.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

Новые названия техпроцессов

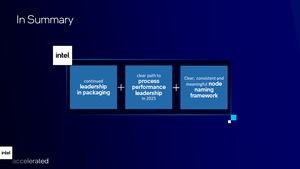

Intel меняет схему именования. Enhanced 10nm SuperFin становится Intel 7, вероятно, по причине упомянутого выше неравенства. Затем следуют Intel 4, Intel 3, Intel 20A и Intel 18A. Так называемые intranodes, то есть небольшие улучшения при одинаковом техпроцессе, больше не упоминаются. Хотя совсем недавно они имели весьма серьезное значение для Intel. Во время представления 10nm SuperFin Intel упомянула, что улучшения 14-нм техпроцесса, начиная от Broadwell и продолжая со Skylake, Kaby Lake, Coffee Lake и Cooper Lake, обеспечили прирост производительности на 5,5, 3,8, 5,8 и 5,9% (21% в сумме). В случае Rocket Lake 14-нм техпроцесс достиг своей кульминации, в том числе и по энергопотреблению.

Теперь Intel решила перейти на более быстрый темп производства, который выглядит следующим образом:

| Intel 7 | Intel 4 | Intel 3 | Intel 20A | Intel 18A | |

| Предыдущее название | Enhanced 10nm SuperFin | 7 nm | 5 nm | - | - |

| Производительность/ ватт | +10-15 % | +20 % | +18 % | - | - |

| Старт производства | Q2 2021 | 2H 2022 | 2H 2023 | 1H 2024 | 2025 |

| Появление первых чипов на рынке | Q3/Q4 2021 | 2023 | - | - | - |

В результате нанометры в названии больше не фигурируют. Техпроцесс 7 нм теперь называется Intel 4, за ним следует Intel 3, а все остальные техпроцессы относятся к эпохе ангстрема, как Intel их называет.

Пока что Intel не раскрывала подробности улучшений Enhanced 10nm SuperFin, который теперь называется Intel 7. Известно, что транзисторы FinFET вновь были оптимизированы. В частности, используются материалы с меньшим сопротивлением, новые технологии с высокой плотностью расположения компонентов, был улучшен и стек металлических проводников. Для Intel 7 заявлено улучшение соотношения производительности на ватт на 10-15%. По техпроцессу Intel 7 будут изготавливаться процессоры Alder Lake для настольных и мобильных рынков, а также Xeon с кодовым названием Sapphire Rapids. Массовое производство уже запущено. Потребительские процессоры выйдут в третьем или четвертом квартале, однако новое поколение Xeon с поддержкой HBM теперь ожидается не раньше 2022. По крайней мере, в случае Sapphire Rapids также будет использоваться EMIB 1.0. Данная технология интерконнекта свяжет четыре кристалла. Расстояние между шариковыми контактами составит всего 55 мкм, поэтому четыре кристалла будут работать как цельный чип. Подробнее мы поговорим об этом чуть ниже.

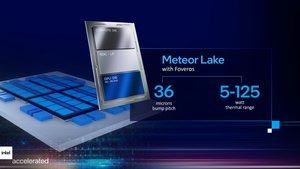

Intel 4 - это техпроцесс, который ранее упоминался как 7 нм. Он будет использоваться для Meteor Lake и Granite Rapids (по крайней мере, для вычислительных кристаллов). Цель заключается в 20% увеличении эффективности. Производство стартует во второй половине 2022 года, но первые продукты не ожидаются раньше 2023. В случае Intel 4 будет использоваться больше слоев с EUV, чем ранее с Intel 7. На диаграмме настольной версии Meteor Lake можно видеть вычислительный кристалл, кристалл SoC и кристалл GPU, который содержит от 96 до 196 EU. TDP Meteor Lake будет составлять от 5 до 125 Вт, как и в случае Alder Lake, так что здесь Intel сможет охватить как экономичные ноутбуки, так и настольные ПК.

В случае Intel 3 подробностей довольно мало. Прирост производительности на ватт составляет 18%. Intel планирует достичь более высокого уровня производительности транзисторов, чем обычно бывает при переходе между разными техпроцессами. Для Intel 3 снова указывается увеличение плотности расположения транзисторов и использование высокопроизводительных библиотек при дизайне чипа, а также оптимизация металлического стека интерконнекта. Также EUV будет использоваться для большего числа слоев. Производство первых чипов по техпроцессу Intel 3 запланировано на вторую половину 2023.

Затем начнется эпоха ангстремов. Один ангстрем - это десятимиллионная часть миллиметра, то есть 0,1 нм. Таким образом, техпроцесс Intel 20A можно назвать 2 нм. Результатов производительности пока нет, но будут использоваться две новых технологии RibbonFET и PowerVia, о которых мы как раз поговорим. Intel планирует начать производство чипов по техпроцессу Intel 20A в первой половине 2024. Затем в 2025 году последует Intel 18A. Intel будет использовать оборудование High-NA (Numerical Aperture) EUV от ASML, которая как раз поставит первую партию Intel.

RibbonFET и PowerVia для эпохи ангстрема

Intel нашла собственное название для транзисторов Gate-all-around (GAA), у которых затвор полностью окружает канальную область. Они будут называться RibbonFET, транзисторы заменяют нынешние FinFET (Field-Effect Transistors). Транзисторы Multi Bridge Channel FETs (MBCFET) могут использовать разные структуры. В случае Intel - это наноленты. Транзисторы GAA можно представить как полевые транзисторы (FET), у которых затвор окружает очень тонкую канальную область с четырех сторон. Подобный шаг позволяет преодолеть ограничения по дальнейшему масштабированию и производительности FinFET, а также снизить рабочее напряжение. Кроме того, транзисторы GAA представляют собой 3D-структуру. Таким образом, RibbonFET может заменить несколько FinFET на меньшей площади. Причем характеристики RibbonFET можно регулировать в зависимости от ширины затвора, которая задается при производстве.

Samsung планирует представить 3-нм техпроцесс MBCFET уже в начале 2022 года для контрактного производства. Intel последует на два года позже.

PowerVia - новая технология подачи питания на чип. До сих пор проводящие дорожки и каналы на кристалле располагались с одной стороны, там же, где и элементы логики, то есть транзисторы. Но при этом могли возникать помехи из-за взаимного влияния множества проводников питания и компонентов логики, то есть металлических слоев транзисторов. Все же следует помнить, что чип содержит несколько миллиардов транзисторов. С помощью PowerVia теперь можно использовать обратную сторону кристалла/подложки. То есть элементы логики и интерконнекты располагаются по-прежнему с лицевой стороны, а компоненты питания уже с противоположной. Причем сквозные проводники TSV для PowerVia будут в 500 раз меньше, чем использующиеся сегодня TSV в корпусировках.

Пока не совсем понятно, как именно будет работать технология. Intel показывает на рисунке обычную структуру FinFET слева и RibbonFET и PowerVia справа. Слева конфигурация вполне типична, при экспозиции подложек она создается слой за слоем. В нижней части расположен зеленый слой - это непосредственно транзисторы. Выше располагаются интерконнекты и питание. Наконец, в верхней части устанавливаются соединения с "внешним миром".

Справа показана структура чипа, который производится по техпроцессу Intel 20A с RibbonFET и PowerVia. Ориентация теперь примерно соответствует тому, как чип расположен на PCB в сокете. В нижней части чипа расположены проводники питания, которые подводятся к тонкому зеленому слою, где находятся сами транзисторы. Выше вновь показан слой интерконнектов, который знаком по обычной конфигурации. Обратите внимание на тонкий серый слой под зеленым слоем транзисторов, он является разделителем между фронтальной и тыловой частями подложки. Вверху вновь располагается толстый слой кремния. В целом, традиционная структура здесь находится как бы "вверх ногами". Пока не совсем понятно, как именно Intel технически реализует экспозицию кристалла с двух сторон.

В будущем на мероприятиях Architecture Day Intel наверняка раскроет больше подробностей RibbonFET и PowerVia. Первые чипы с техпроцессом Intel 20A и упомянутыми технологиями будут производиться только в 2024 году.

Чтобы показать отличия в структуре транзисторов на чипе, мы привели три вида на картинке ниже.

Улучшения дизайна FinFET связаны со структурой самого транзистора. Например, Intel изменила размеры затвора, стока и истока, чтобы можно было уменьшить напряжение или увеличить скорость переключения. В случае же транзисторов GAA полностью меняется структура, как можно видеть на примере RibbonFET. Несколько ленточных канальных областей расположены друг над другом, они полностью окружены затвором. Что улучшает эффективность управления затвором и производительность транзистора.

По сравнению с FinFET, RibbonFET могут работать с более высоким током. Впрочем, не только Intel планирует представить GAA в качестве преемника FinFET, но и Samsung и TSMC - они предложат свои техпроцессы в ближайшие годы.

Мы привели сравнение слоев двух вариантов FinFET и RibbonFET с PowerVia. Между Intel 10 и Intel 7 произошли оптимизации по металлическим слоям. В случае же Intel 20A используется новый способ подведения питания.

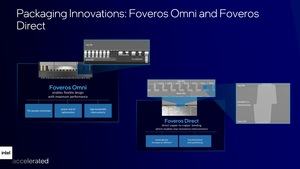

Foveros 2.0 превращается в Foveros Omni и Foveros Direct

Intel планирует вернуть былую силу через год-два не только по производству полупроводников. Компания намеревается выйти в лидеры по технологиям корпусировки. В частности, здесь стоит упомянуть технологии EMIB и Foveros.

Foveros использовалась с процессорами Lakefield, которые уже не производятся. Что касается EMIB, то она впервые нашла применение в процессорах Core с графикой Radeon RX Vega M. EMIB первого поколения с расстоянием между шариковыми контактами 55 мкм будет использоваться и для Sapphire Rapids, то есть нового поколения Xeon. У EMIB 2.0 расстояние между шариковыми контактами составляет 45 мкм, что позволит увеличить плотность расположения интерконнекта и пропускную способность интерфейсов.

Foveros - вторая технология, которая используется в корпусировках Intel. И для второго поколения Foveros Intel решила разделить ее на Foveros Omni (соединение множества разных кристаллов в корпусировке 2.5D) и Foveros Direct (соединение кристаллов с одинаковым техпроцессом). Обе технологии будут использоваться в собственных продуктах Intel, а также для проектов Foundry. Intel указывает расстояние между шариковыми контактами Foveros Omni на уровне 25 мкм. У первого поколения Foveros оно составляло 36 мкм.

Foveros Direct несколько напоминает стек SRAM, который AMD использует для 3D V-Cache. Но у AMD применяется технология стекирования SoIC от TSMC. Intel для Foveros Direct тоже планирует прямое соединение с шариковыми контактами, как и в случае TSMC SoIC. Причем расстояние между шариковыми контактами будет снижено до 10 мкм.

Ускоритель Ponte Vecchio HPC как раз первым будет использовать первое поколение Foveros и второе EMIB.

Qualcomm и Amazon - первые клиенты Intel

Анонс Intel начался с инициативы IDM 2.0, ею и закончился. Первым контрактным клиентом Intel станет Qualcomm, который будет производить чипы по техпроцессу Intel 20A. А Amazon планирует воспользоваться технологиями корпусировки Intel для своих процессоров для дата-центров.

Наконец, предлагаем посмотреть несколько видеороликов, опубликованных Intel, на которых показаны обновленные технологии EMIB, Foveros и новые RibbonFET и PowerVia.