На прошлой неделе Intel рассказала подробности грядущих процессоров Alder Lake и поделилась амбициозными планами по производству дискретных GPU на основе Xe-HPG, которые выйдут под брендом Intel Arc в начале 2022.

На прошлой неделе Intel рассказала подробности грядущих процессоров Alder Lake и поделилась амбициозными планами по производству дискретных GPU на основе Xe-HPG, которые выйдут под брендом Intel Arc в начале 2022.

На мероприятии Architecture Day 2021 Intel также рассказала о грядущем поколении Xeon под названием Sapphire Rapids, а также своих амбициях в сфере HPC, ускорителях Xe-HPC или Ponte Vecchio с большим количеством тайлов в крупной корпусировке. На конференции Hot Chips мы смогли разузнать новые подробности, что позволяет подвести итог. Ниже мы приведем известную информацию о Ponte Vecchio и Sapphire Rapids.

Новое поколение Xeon Sapphire Rapids

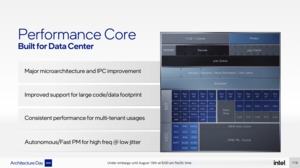

До сих пор Intel весьма неохотно делилась информацией насчет Sapphire Rapids. Но на Architecture Day информационный поток оказался весьма обильным. Новое поколение Xeon опирается на производительные ядра Alder Lake на основе Willow Cove. В полной версии данные ядра предлагают все необходимые расширения для серверного сегмента, а именно AVX-512, AMX (Advanced Matrix Extensions) и FP16.

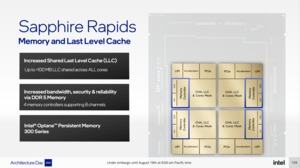

Кроме того, для всех ядер доступен кэш LLC до 100 Мбайт. Отметим поддержку CXL 1.1, DDR5, PCI Express 5.0 и опциональное подключение HBM, что позволит Sapphire Rapids выйти в лидеры серверного рынка. Intel пока не объявила конкретные продукты, но рассказала о производстве.

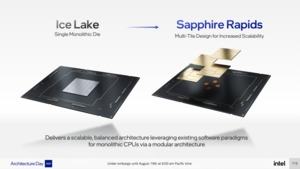

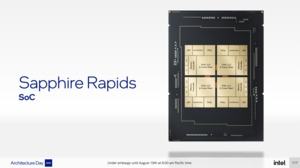

Xeon на ядрах Sapphire Rapids использует четыре тайла. Каждый тайл содержит ядра CPU, кэш LLC, контроллер памяти для двух каналов и компоненты ввода/вывода. В общей сложности на платформе Sapphire Rapids доступны восемь каналов памяти DDR5, каждый тайл обеспечивает как раз два канала. Но Intel сможет поддержать все восемь каналов памяти только при условии активности всех четырех тайлов. Количество активных ядер на тайл зависит от модели процессора Xeon.

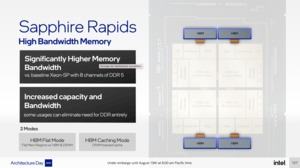

Intel планирует оснастить некоторые модели HBM. Официальное подтверждение появилось несколько недель назад. Intel планирует использовать четыре стека памяти, но пока что не раскрывает емкость или пропускную способность. По крайней мере, известно, что HBM может работать в двух режимах. В HBM Flat Mode обычная оперативная память не требуется, все данные хранятся в HBM. В случае же HBM Caching Mode память HBM работает как кэш доступа к памяти DDR5.

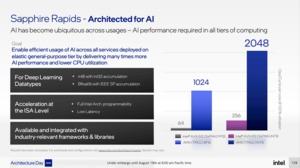

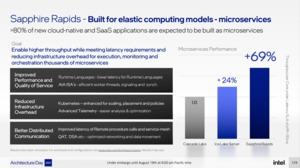

Вместе с функциональными блоками AVX-512 и AMX, скоростная память HBM призвана обеспечить высокую производительность Xeon в сфере искусственного интеллекта. Впрочем, и в обычных приложениях производительность должна существенно увеличиться. Для Sapphire Rapids прирост производительности по сравнению с Cascade Lake составит до 69%.

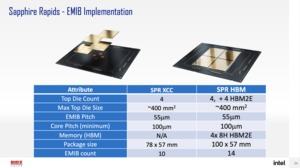

Процессоры Xeon Sapphire Rapids производятся по техпроцессу Intel 7, который ранее назывался 10nm Enhanced SuperFin. Кристалл XCC (Extreme Core Count) имеет площадь 400 мм². Как упоминалось выше, в одной корпусировке используются до четырех таких чипов, что дает суммарную площадь 1.600 мм². Десять интерфейсов EMIB (Embedded Multi-die Interconnect Bridge) соединяют четыре тайла друг с другом. Поэтому равенства интерфейсов между тайлами нет: как мы узнали, будут использоваться варианты 2x2 и 2x3.

Если добавить четыре чипа памяти HBM, то Intel придется опираться на 14 интерфейсов EMIB, по одному дополнительному на каждый стек HBM. Пока что Intel дает противоречивые сведения о размере корпусировки, но, по нашей информации, оба варианта устанавливаются в одинаковый сокет, то есть их можно свободно заменять, если можно так выразиться.

Процессоры Sapphire Rapids выходят в первом квартале 2022. Intel ближе к этому времени поделится новыми подробностями и объявит конкретные модели.

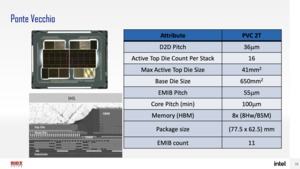

HPC-ускоритель Ponte Vecchio

HPC-ускоритель Ponte Vecchio является для Intel вопросом престижа. Информации здесь тоже очень немного, общую картину нарисовать сложно, но мы попытаемся. Intel частично открыла завесу тайны, рассказав о структуре ускорителя.

На нижнем уровне используются ядра Xe. Они представляют собой вариант архитектуры Xe (Xe-HPC), адаптированной под HPC. Ядра Xe содержат по восемь векторных блоков (шириной 512 бит) и восемь матричных движков (4.096 бит). Кэш L1 на ядро Xe составляет 512 кбайт. В зависимости от размера входных данных, векторный блок может выполнять 256 или 512 операций за такт (256 FFP32 и FP64, 512 FP16). Для матричных движков заявлена производительность 2.048 (TF32), 4.096 (FP16 и BF16) или 8.192 (INT8).

На более высоком уровне ядра Xe объединены в слайсы. Соответственно, 16 ядер Xe составляют один слайс, к ним добавляются блоки трассировки лучей, которые больше интересны для игровых вариантов Xe HPG. Стек состоит из четырех слайсов, он добавляет кэш L2, а в случае Xe-HPC четыре контроллера памяти HBM2E и восемь каналов Xe для соединения нескольких стеков. На данный момент в планах Intel значится объединение двух стеков. Вариант с четырьмя стеками теоретически возможен, но Ponte Vecchio подразумевает два стека.

Структура корпусировки получается довольно сложной. Имеются вычислительные ядра со слайсами и кэш Rambo, который устанавливается между слайсами через Foveros. Все это располагается на базовом тайле (base tile).

Дополнительные тайлы - это интерфейсы Xe Link, упомянутые выше, и HBM. Соединение осуществляется через EMIB. В итоге тайлы соединяются в рамках одной большой корпусировки Multi Tile Package. Речь идет о 47 активных тайлах, которые производятся по пяти разным техпроцессам.

Intel особо подчеркивает вычислительные тайлы, выпускаемые по 5-нм техпроцессу на TSMC. Базовый тайл изготавливается по техпроцессу Intel 7 (10nm Enhanced SuperFin). Тайлы Xe Link вновь производятся TSMC, но уже по 7-нм техпроцессу. Насчет кэша Rambo Intel пока не раскрывает деталей производства. Скорее всего, здесь тоже будет использоваться Intel 7. Остаются кристаллы HBM2E, которые будут производиться Samsung или SK Hynix.

Что касается корпусировки, Intel намеревается использовать множество соединений EMIB и Foveros. Вариант с двумя стеками опирается на 11 интерфейсов EMIB (пять на стек: 4x HBM + 1x Xe Link) и один между двумя стеками. Что касается слайсов в стеке, они подключаются 16 интерфейсами Foveros.

Как и в случае Sapphire Rapids, подробностей конкретных Ponte Vecchio пока нет. На конференции Architecture Day Intel объявила базовую архитектуру и конфигурацию. По мере приближения к дате анонса процессоров и HPC-ускорителей мы наверняка узнаем подробности.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).