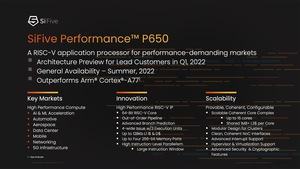

Через несколько дней стартует конференция RISC-V Summit, но разработчик SiFive решил официально представить Performance Core P650. Как обещает SiFive, производительность нового ядра соответствует уровню Cortex-A77 от ARM.

Через несколько дней стартует конференция RISC-V Summit, но разработчик SiFive решил официально представить Performance Core P650. Как обещает SiFive, производительность нового ядра соответствует уровню Cortex-A77 от ARM.

SiFive утверждает, что на рынке нет более быстрого ядра RISC-V общего назначения. В зависимости от конфигурации кластера, каждое ядро оснащается до 256 кбайт кэша L1 (по 128 кбайт для данных и инструкций).

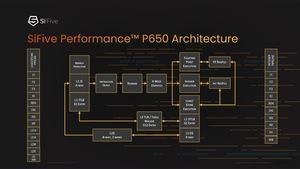

В одном кластере можно устанавливать уже не до четырех ядер P550, а до 16 новых P650. Соответственно общий кэш L3 может составлять до 16 Мбайт. Емкость кэша L2, эксклюзивного для ядер, достигает 2 Мбайт. Похоже, по структуре ядер изменений немного, как и по вычислительным блокам. Конвейер глубиной 13 ступеней поддерживает внеочередное выполнение.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

| P550 | P650 | |

| Кэш инструкций L1 | 32 кбайт | 64-128 кбайт |

| Кэш данных L1 | 32 кбайт | 64-128 кбайт |

| Кэш L2 | 256 кбайт | до 2 Мбайт |

| Кэш L3 | 1 - 4 Мбайт | 1 - 16 Мбайт |

| Core Complex | до 4 ядер | до 16 ядер |

| Memory Ports | 1x 128 или 256 бит | 4x 128 или 256 бит |

RISC-V Foundation разработало 15 новых спецификаций, которые ядра P650 будут поддерживать. В общей сложности RISC-V ISA поддерживает 40 новых инструкций, но их число все равно сравнительно невелико. В P650 впервые поддерживается гипервизор и виртуализация, что расширяет сферу использования. Но есть инновации по векторным расширениям и криптографии.

Ядра P650 переносят архитектуру RISC-V на новые сегменты, причем они становятся более интересны и для обычных потребителей. Благодаря усилиям разработчиков производительность (на равных тактовых частотах) достигла уровня Cortex-A77. Сфера применения теперь расширяется от устройств IoT до серверов, по крайней мере, в теории. SiFive представит первые тестовые ядра на P650 выбранным клиентам в первом квартале 2022. А летом дизайн будет открыт всем желающим.

Благодаря объединению кластеров можно получить дизайн до 128 ядер. Кроме кластеров CPU через интерконнект Network on Chip (NOC) соединяются компоненты безопасности, кэш последнего уровня и движок трансляции. В результате получается довольно сложный чип с несколькими каналами памяти (LP)DDR, многочисленными контроллерами PCIe и линиями, а также внешним подключением CXL через SiFive Chip2Chip Link.

Также мы рекомендуем ознакомиться с нашими тестами SiFive HiFive Unmatched, платформы для разработчиков RISC-V.