Процессоры Ryzen с кэшем 3D V-cache, вернее, единственная модель Ryzen 7 5800X3D, пока только планируются, в продажу они еще не поступили, но AMD рассказала на ISSCC 2022 некоторые подробности реализации, в том числе ранее неизвестные.

Процессоры Ryzen с кэшем 3D V-cache, вернее, единственная модель Ryzen 7 5800X3D, пока только планируются, в продажу они еще не поступили, но AMD рассказала на ISSCC 2022 некоторые подробности реализации, в том числе ранее неизвестные.

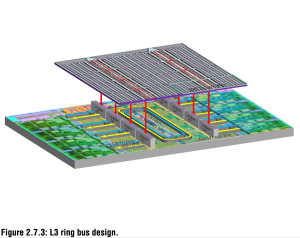

Напомним, что самым большим изменением иерархии кэшей Zen 3 стал общий кэш L3 емкостью 32 Мбайт для восьми ядер. Ранее он был разделен на кристалле CCX (core compute complex) на две половинки по 16 Мбайт. Теперь субслайсов стало восемь, а не четыре, соответствующий интерконнект был переведен на двунаправленную кольцевую шину, передающую информацию со скоростью 32 байт на такт. Более высокая пропускная способность с меньшими задержками привела к тому, что архитектура Zen 3 достигла целей по производительности. Каждое ядро теперь получило доступ к полным 32 Мбайт кэша L3. Но по производству кэша L3 тоже произошли изменения. AMD использовала битовые ячейки с высокой плотностью High Density (HD) вместо ячеек с высоким током High Current (HC) ранее. Что позволило сэкономить 14% площади, а также уменьшить токи утечки кэша на 24%.

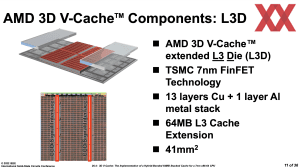

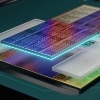

Но AMD оставила себе лазейку, которая ранее не использовалась. Кэш L3 можно было расширить с 32 до 96 Мбайт через дополнительный чип SRAM. Чип кэша площадью всего 36 мм², устанавливался на область L3 кристалла CCD и соединялся медными проводниками. Эффекта адгезии между двумя кристаллами было достаточно для надежного крепления, припаивания не требовалось.

Соединение между основным кэшем на кристалле и дополнительным выполняется через сквозные проводники TSV. Для этого AMD предусмотрела два ряда соединений TSV. Каждый участок кэша 3D V-cache объемом 8 Мбайт соединяется 1.024 контактами. В итоге между CCX и кэшем 3D V-cache используется 8.192 контактов.

Интерфейс TSV обеспечивает пропускную способность более 2 Тбит/с на слайс. Кольцевая шина кэша L3 дает больше 2 Тбайт/с в двух направлениях, поэтому проблем с пропускной способностью кэша L3 для всех ядер не возникнет даже с дополнительным кэшем 3D V cache.

Дополнительные улучшения техпроцесса

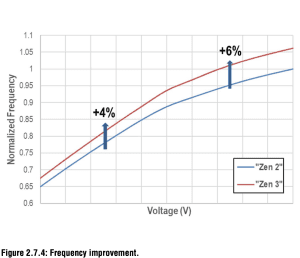

7-нм техпроцесс TSMC был оптимизирован так, чтобы 13 нижних слоев обеспечивали более высокую плотность, а верхние слои - максимально возможные частоты. Цель заключалась в увеличении частот на 4% при сохранении прежних напряжений. Для пиковой однопоточной производительности есть возможность подачи на 6% более высокого напряжения.

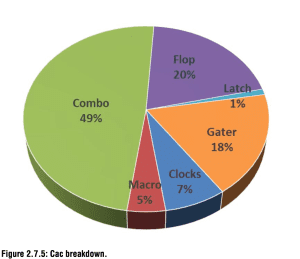

В архитектуре Zen 3 AMD попыталась изменить структуру логических блоков, комбинируя ячейки HC и HD, описанные выше. Также были оптимизированы соединения, чтобы обеспечивать более высокие частоты на высоких напряжениях. Чтобы получить прирост 19% IPC и 6% частоты, AMD увеличила CCX Effective Switched Capacitance (Cac) на 15%.

Доля Cac, уходящая на работу затворов, была немного увеличена по сравнению с предыдущим поколением. Процент Cac на Flops и комбинационную логику был немного снижен из-за дополнительной оптимизации затворов по эффективности в архитектуре Zen 3. Токи утечки немного возросли, но это было компенсировано ростом частот и дальнейшими улучшениями эффективности энергопотребления.

AMD очень гордится своей архитектурой Zen 3, особенно в ракурсе возможного расширения кэша L3.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).