На конференции Future Summits 2022 главный исполнительный директор Imec (Interuniversity Microelectronics Centre) Люк Ван рассказал о препятствиях и возможных решениях по производству чипов с размером компонентов 1 нм и меньше, которые связывают с эпохой ангстрема. Данный термин уже взяла на вооружение Intel с техпроцессами Intel 20A и Intel 18A, наверняка его начнут использовать и другие производители полупроводников в ближайшие годы.

На конференции Future Summits 2022 главный исполнительный директор Imec (Interuniversity Microelectronics Centre) Люк Ван рассказал о препятствиях и возможных решениях по производству чипов с размером компонентов 1 нм и меньше, которые связывают с эпохой ангстрема. Данный термин уже взяла на вооружение Intel с техпроцессами Intel 20A и Intel 18A, наверняка его начнут использовать и другие производители полупроводников в ближайшие годы.

Новые материалы, прогресс по технологиям экспонирования, разработка новых техпроцессов с меньшими размерами структур, а также продолжающееся увеличение плотности интеграции компонентов позволяют продлить действие закона Мура. Imec – один из самых крупных исследовательских центров в индустрии полупроводников. В принципе, информация доклада во многом пересекается с тем, что мы слышали в последнее время от Intel, ASML, TSMC, Samsung и других.

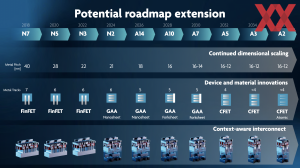

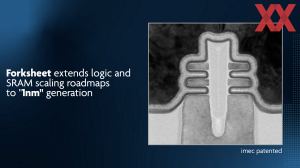

Презентация началась с описания новых разрабатываемых техпроцессов. Транзисторы FinFET верой и правдой служили многие годы, но с техпроцессов 2-3 нм и меньше они уже не имеют никаких перспектив. Следующая технология – транзисторы с окружающим затвором (GAA, gate all-around), Samsung уже начала в этом году массовое производство. Начиная с Intel 20A, чиповый гигант переведет производство на новый тип транзисторов RibbonFET. Здесь подразумевается как стек из нескольких транзисторов, так и другие варианты интеграции. В дизайне forksheet канальные области p и n транзистора располагаются очень близко, их разделяет тонкая стенка диэлектрика. Данный транзистор значительно улучшил свои характеристики, но возникает проблема изготовления структур очень маленького размера.

К 2028-2030 году Imec прогнозирует переход на транзисторы forksheet. Причем тогда мы уже войдем в эпоху ангстрема. Напомним, что один ангстрем – это десятимиллионная часть миллиметра, то есть 0,1 нм.

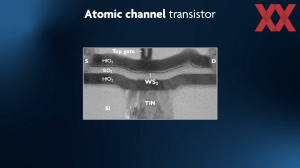

С 2032 года будут использоваться транзисторы CFET (Combined fets). Здесь дизайн forksheet будет стекироваться в вертикальной плоскости. Данные техпроцессы сегодня находятся на стадии исследования, поскольку необходимо найти новые материалы, из которых получится создавать структуры толщиной в несколько атомов. Из потенциальных кандидатов называют рутений и дисульфид вольфрама (WS₂), с их помощью можно уменьшить токи утечки, если получится использовать их в качестве изолятора.

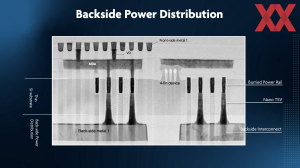

Кроме того, структура чипа будет меняться. Сегодня подложки экспонируются с одной стороны. В будущем экспонирование будет выполняться с двух сторон, что позволит дополнительно наносить линии питания и передачи данных. Сначала будут экспонироваться транзисторы и линии передачи данных, затем к кристаллу добавляются сквозные проводники TSV и линии питания. Все это существенно увеличивает сложность. Intel называет данную технологию PowerVia. TSMC, Samsung и другие производители придумали свои термины.

Все это позволяет плотнее упаковывать транзисторы, повышая плотность. С другой стороны, улучшается целостность и качество сигналов, что упрощает структуру.

3D-чипы и гигантские машины экспонирования

Следующий шаг, который мы видим в современных чипах, заключается в стеке разных дизайнов. AMD уже устанавливает кристаллы SRAM на свои ядра. Intel устанавливает базовый тайл с компонентами ввода/вывода и кэша в дизайне Ponte Vecchio. И данный способ будет становиться все более популярным.

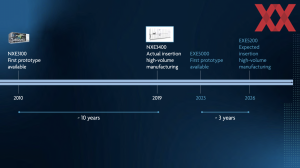

Не стоит забывать о производителях оборудования по производству полупроводников. Лидером индустрии здесь является ASML. Переход на High NA (high-numerical aperture) EUV позволит уменьшить минимально возможное расстояние между проводниками (metal pitch) до 12 нм.

Первые машины high-NA EUV начнут устанавливаться в 2023 году. В 2026 году ожидается старт массового производства чипов на них. Причем ASML работает уже над следующим поколением, поскольку разработка подобных машин занимает не меньше десяти лет.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).