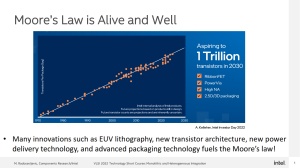

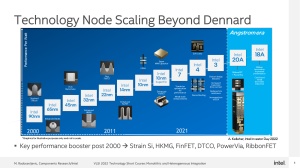

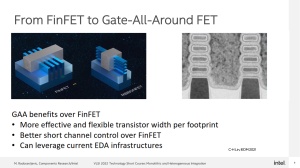

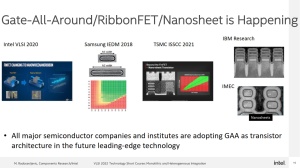

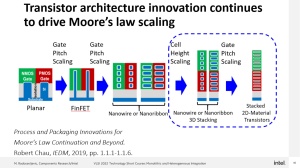

На конференции VLSI Symposium Intel рассказала подробности новых типов транзисторов. Начиная с техпроцесса Intel 20A, который запускается в 2024/25 годах, нас ждет фундаментальное изменение структуры транзисторов. Все крупные производители полупроводников сегодня работают над транзисторами GAA (Gate-All-Around) с затвором, окружающим канальную область. Транзисторы GAA заменят старые добрые FinFET, причем Intel называет их RibbonFET, подразумевая еще и стек транзисторов.

На конференции VLSI Symposium Intel рассказала подробности новых типов транзисторов. Начиная с техпроцесса Intel 20A, который запускается в 2024/25 годах, нас ждет фундаментальное изменение структуры транзисторов. Все крупные производители полупроводников сегодня работают над транзисторами GAA (Gate-All-Around) с затвором, окружающим канальную область. Транзисторы GAA заменят старые добрые FinFET, причем Intel называет их RibbonFET, подразумевая еще и стек транзисторов.

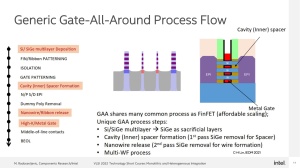

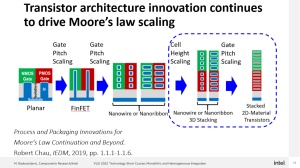

Первое поколение транзисторов GAA будет состоять из полупроводников NMOS и PMOS с затворами, окружающими тонкие канальные области со всех четырех сторон. В случае широких канальных областей они называются наноленты, узких – нанопровода. Подобные затворы позволяют преодолеть физические ограничения масштабирования и мощности FinFET, что позволит и дальше масштабировать напряжение питания.

Еще одно преимущество транзисторов GAA в том, что они могут пропускать такой же ток, что и несколько FinFET, причем на существенно меньшей площади. Свойства транзисторов можно гибко регулировать через ширину затворов при производстве.

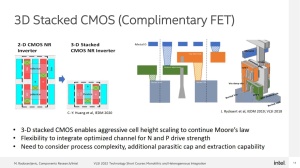

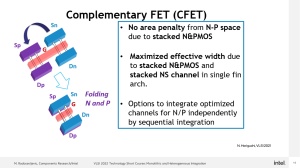

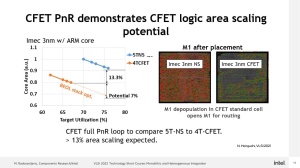

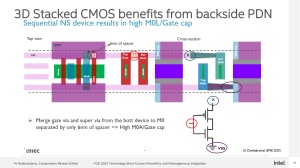

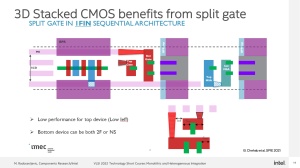

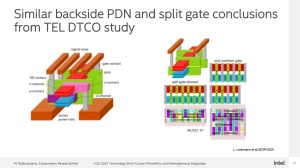

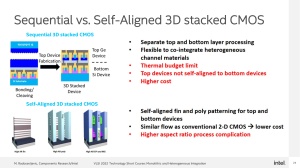

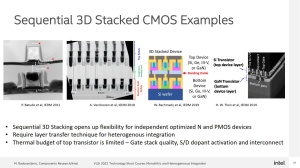

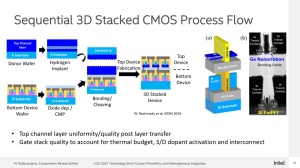

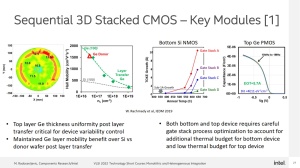

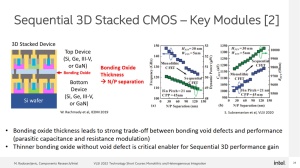

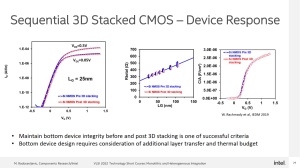

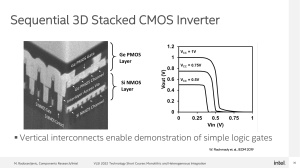

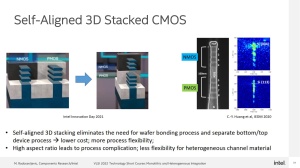

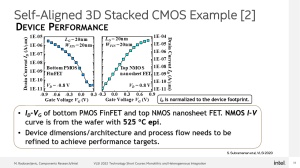

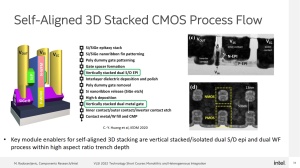

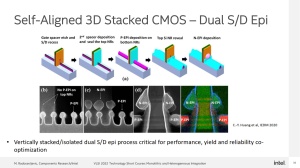

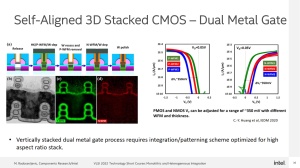

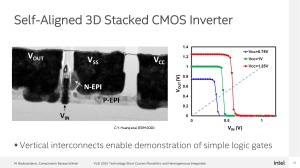

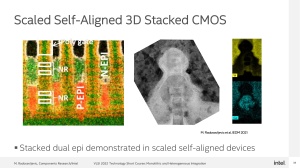

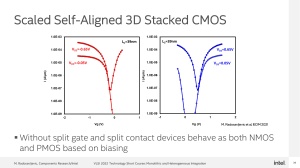

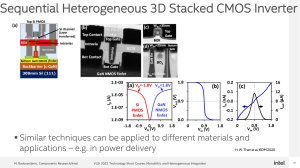

Следующим шагом Intel планирует сделать стек областей NMOS и PMOS друг на друге. Что должно уменьшить площадь, занимаемую на чипе, на 30-50%. Intel работает над разными вариантами стеков NMOS и PMOS. Например, последовательный процесс с германиевыми транзисторами PMOS GAA на кремниевых NMOS FinFET или цельный (self-aligned) техпроцесс с NMOS-on-PMOS multi-RibbonFET транзисторами с шагом между затворами (poly pitch) всего 55 нм.

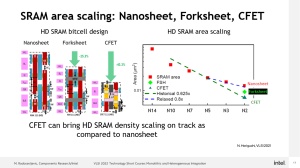

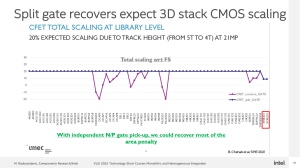

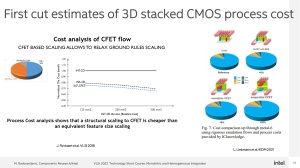

Complementary FETs (CFET) представляют собой «согнутые» транзисторы N&P MOS в целях уменьшения занимаемой площади, при этом они намного проще транзисторов GAA. Подобные транзисторы будут использоваться в высокоплотных ячейках памяти SRAM, что позволит добиться рекордной плотности расположения ячеек. Ячейка HD из нанолистов почти в два раза крупнее, чем сравнимая ячейка памяти на основе CFET.

Транзисторы GAA лучше всего подходят для схем логики, а CFET будут применяться для SRAM, чтобы и дальше обеспечить масштабирование. И это лишь один из примеров использования разных технологий транзисторов при производстве процессора. Вместе применяются и разные типы транзисторов, и типы библиотек, оптимизированные под свою специфическую область.

Конечно, стек транзисторов приводит к дополнительным шагам при производстве. Поэтому придется оптимизировать сложность и затраты. Соответствующие команды в Intel работают над этим многие годы.

Для некоторых высокопроизводительных библиотек стеки транзисторов не подходят из-за проблем с тепловыделением. Здесь будут применяться транзисторы Self-Aligned 3D Stacked Multi-Ribbon CMOS.

Первыми этапами для Intel станут техпроцессы Intel 4 и Intel 3. На конференции VLSI чиповый гигант как раз поделился подробностями техпроцесса Intel 4. Но техпроцесс Intel 4 является лишь промежуточным шагом на пути к Intel 3. Для Intel 4 чиповый гигант не собирается выпускать библиотеки HD и I/O. Данный техпроцесс ориентирован на кристаллы с вычислительной логикой и ядрами, но не на кэши. В случае Meteor Lake подобная ориентация будет хорошо видна, поскольку по техпроцессу Intel 4 будет выпускаться только вычислительный тайл. Техпроцесс Intel 3, с другой стороны, будет оптимизирован и под другие типы тайлов.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).

Мы рекомендуем ознакомиться с нашим руководством по выбору лучшего процессора Intel и AMD на текущий квартал. Оно поможет выбрать оптимальный CPU за свои деньги и не запутаться в ассортименте моделей на рынке.