На конференции 2022 Technology Symposium TSMC раскрыла свои планы по производству полупроводников на ближайшие три года. Основой производства станет 3-нм техпроцесс. Чтобы лучше оптимизировать его под потребности клиентов, а также сократить дистанцию до технологии нанолистов, кроме N3 будут введены еще четыре разных 3-нм техпроцесса.

На конференции 2022 Technology Symposium TSMC раскрыла свои планы по производству полупроводников на ближайшие три года. Основой производства станет 3-нм техпроцесс. Чтобы лучше оптимизировать его под потребности клиентов, а также сократить дистанцию до технологии нанолистов, кроме N3 будут введены еще четыре разных 3-нм техпроцесса.

Современное полупроводниковое производство становится все сложнее и дороже. Поэтому контрактные производители полупроводников увеличивают сроки эксплуатации техпроцессов, а также длительность разработки. Кроме того, далеко не каждому клиенту нужны самые современные техпроцессы. Поэтому в ближайшие годы TSMC будет диверсифицировать производство.

Кроме запущенного 3-нм техпроцесса, TSMC предложит варианты N3E, N3P, N3S и N3X в 2023, 2024 и 2025 годах. Массовое производство по техпроцессу N3 (High Volume Manufacturing, HVM) запланировано на вторую половину 2022 года, а первые чипы ожидаются в 2023. Клиенты, которые всегда пытаются взять максимум от современных техпроцессов по характеристикам PPA (производительность, энергопотребление, площадь), готовы платить соответствующую цену. Конечно, кандидатом номер один здесь будет Apple.

Техпроцесс N3E уже был анонсирован ранее. У техпроцесса N3E можно ожидать улучшения по производительности и/или по снижению энергопотребления. Но плотность расположения транзисторов существенно увеличивать не планируется. Здесь N3E не даст весомых преимуществ по сравнению с N3. Опытное производство чипов по техпроцессу N3E начнется в ближайшие годы, а массовое HVM – в середине 2023.

N3S и N3X для специальных решений

N3P будет оптимизированным N3 под производительность, а N3S даст улучшения по плотности расположения транзисторов. TSMC здесь не дает точных подробностей, но техпроцессы N3P и N3S ожидаются не раньше 2024 года.

Техпроцесс N4X является производительным вариантом N4, такая же судьба уготовлена N3X. Техпроцессы X рассчитаны на высокие токи и напряжения, поэтому они способны дать рекордную производительность в случаях, когда энергопотребление не имеет значения. Однако пока нет информации, какой прирост производительности обеспечит N3X.

Технология FinFlex

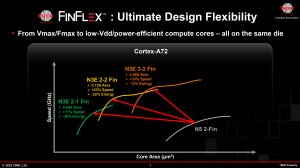

Если разнообразия N3, N3E, N3S, N3P и N3X будет недостаточно, TSMC представила еще одну опцию в виде технологии FinFlex, позволяющую адаптировать техпроцесс под специфические нужды клиентов. Конечно, речь идет только о крупных клиентах, которые заказывают несколько тысяч подложек с сотнями тысяч чипов. Например, TSMC может адаптировать техпроцессы под NVIDIA и AMD.

Технология FinFlex как раз обеспечивает должную гибкость, клиент получает больше возможностей оптимизировать процесс производства под себя.

Современные процессоры уже давно делаются из разных типов транзисторов. Так называемые библиотеки для схем логики разрабатываются под максимальную производительность в расчете на такт с минимально возможным энергопотреблением. А у транзисторов SRAM и кэша в приоритете максимальная плотность.

TSMC описывает технологию FinFlex на примере техпроцесса N3E. У N3E 2-1 Fin имеется наибольший потенциал по минимизации занимаемой площади и снижению энергопотребления, но прирост производительности небольшой. Техпроцесс N3E 2-2 Fin по параметрам PPA занимает среднее положение. Наконец, техпроцесс N3E 3-2 Fin отличается небольшой плотностью расположения транзисторов, меньшим потенциалом по снижению энергопотребления, но прирост производительности самый высокий.

На иллюстрации показана структура SoC с разными библиотеками. Для производительных ядер выбран техпроцесс 3-2 FinFET, для эффективных - 2-1 FinFET, а для других блоков IP в составе SoC (I/O, например), уже 2-2 FinFET.

N2 – следующая крупная цель

На 2024/2025 TSMC планирует переход с FinFET на транзисторы GAA, которые будут опираться на нанолисты. Подробностей пока нет, но, как и в случае Intel и Samsung, использование новых типов транзисторов приведет к структурным изменениям чипа. Очень много внимания уделяется линиям подведения питания к транзисторам (в случае Intel они называются PowerVia). Что усложняет не только структуру чипа, но и производство в целом. В ближайшие годы мы наверняка получим подробности.

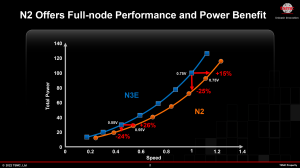

Для N2 TSMC планирует снизить энергопотребление на 25-30% по сравнению с N3E. Производительность увеличится на 15-26%. Кроме того, TSMC обещает увеличить плотность расположения транзисторов в 1,1 раза. Что кажется небольшим, хотя здесь идет сравнение с уже оптимизированным техпроцессом N3E. Также отметим, что TSMC подразумевает на графике смесь 50% логических областей, 30% SRAM и 20% аналоговых компонентов. Как раз аналоговые компоненты очень плохо уменьшаются с нынешними техпроцессами. Поэтому к фактору 1,1 не стоит относиться скептически.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).

Мы рекомендуем ознакомиться с нашим руководством по выбору лучшего процессора Intel и AMD на текущий квартал. Оно поможет выбрать оптимальный CPU за свои деньги и не запутаться в ассортименте моделей на рынке.