Intel вместе с некоторыми партнерами (Dell, Fujitsu, IONOS, VMWare и другие) отпраздновала анонс четвертого поколения Xeon с кодовым названием Sapphire Rapids на конференции в Мюнхене. Мы получили возможность пообщаться с Лизой Спелман, вице-президентом и старшим менеджером подразделения Xeon and Memory Group в Intel. Ниже мы приведем самые интересные ответы, которые получили в ходе интервью. А также поделимся некоторыми другими подробностями.

Intel вместе с некоторыми партнерами (Dell, Fujitsu, IONOS, VMWare и другие) отпраздновала анонс четвертого поколения Xeon с кодовым названием Sapphire Rapids на конференции в Мюнхене. Мы получили возможность пообщаться с Лизой Спелман, вице-президентом и старшим менеджером подразделения Xeon and Memory Group в Intel. Ниже мы приведем самые интересные ответы, которые получили в ходе интервью. А также поделимся некоторыми другими подробностями.

С поколением Sapphire Rapids в фокусе встроенные ускорители – они могут обрабатывать некоторые нагрузки намного быстрее и вместе с тем освобождают ресурсы ядер CPU для других задач. Продолжит ли Intel выбранное направление со следующим поколением вплоть до Falcon Shores?

Как сообщила Лиза Спелман, ускорители действительно используются более широко, но интеграция их непосредственно в процессор стала крупным шагом при разработке Sapphire Rapids, который еще несколько лет назад казался невозможным. Такие ускорители, как QAT, ориентированы на весьма специфические сценарии, но Intel уже показала, что в сотрудничестве с партнерами и пользователями можно сделать намного больше. Ускорение ИИ через AVX-512 (AVX-512_VNNI) было лишь началом и сформировало базу. С каждым поколением Xeon планируются улучшения по ускорителям, как по поддержке каких-либо конкретных сценариев и приложений, так и по количеству.

Как Intel определяет, какие именно ускорители нужны для будущих поколений Xeon?

Intel постоянно общается с клиентами и пытается сделать прогноз. Конечно, проблема «курицы и яйца» никуда не делась, но ее можно начать решать с одной стороны. Отзывы пользователей очень важны для Intel, в том числе для планирования новых поколений. Хорошим примером можно назвать AVX-512: первое время этот набор инструкций критиковали, но сегодня он стал стандартом, который все чаще используется. Та же AMD тоже встроила поддержку AVX-512 в свою архитектуру. Между тем инструкции AVX-512 получили серьезное расширение через VNNI, что продолжается с AVX-512_vRAN.

На предыдущем мероприятии Xeon в Хилсборо Лиза Спелман рассказала о расширенных тестах и процессе валидации Sapphire Rapids. Насколько серьезные изменения произошли по сравнению с предыдущими поколениями?

Конечно, Intel проводила расширенные тесты и валидацию и с предыдущими поколениями. Но гиперскейлеры, как и рынок в целом, выросли за последние несколько лет, они перешли на более крупные и сложные системы. Все более важную роль играет число дефектов в расчете на миллион транзакций (Defects per million, DPM). И при работе сотен тысяч процессоров в системах Facebook, Microsoft и других крупных компаний, каждый с десятком ядер, уровень дефектов становится ощутимым. Два года назад появились первые исследования, которые провела, в том числе Google (Капризные ядра: исследовали комментируют скрытые ошибки CPU).

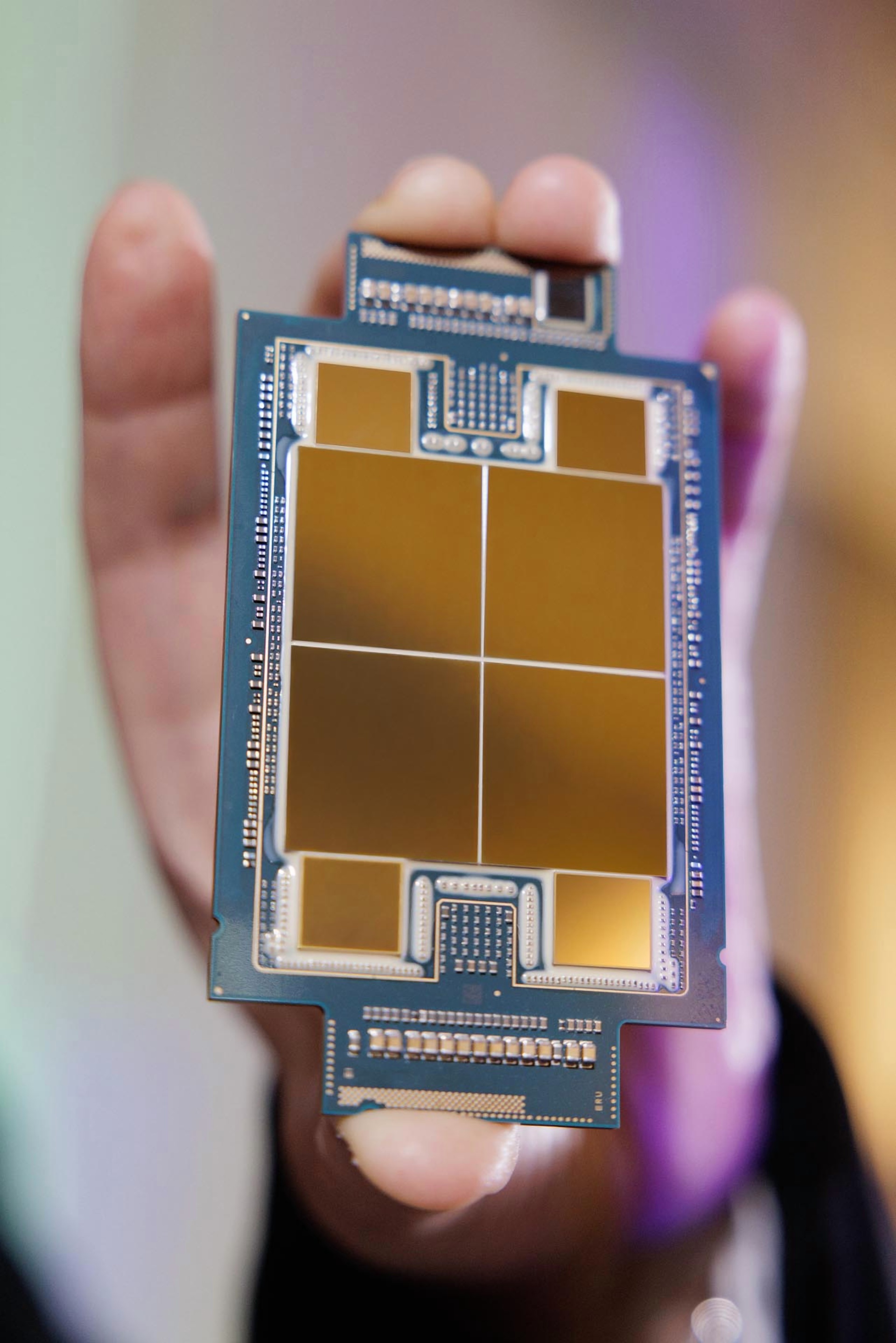

Именно здесь процессоры Sapphire Rapids должны показать себя лучше. В Хилсборо крупные партнеры Intel могут заранее протестировать свои нагрузки. В том числе и на системе Borealis, которая является тестовым вариантом суперкомпьютера Aurora класса экзаскейла. Ранее мы смогли посетить лабораторию Intel HPC и рассказали о системе Borealis. Она опирается на процессоры Sapphire Rapids, которые также будут использоваться и в суперкомпьютере Aurora. То же самое касается GPU-ускорителей Ponte Vecchio. На следующем этапе в тестовую систему будут устанавливаться процессоры Sapphire Rapids с памятью HBM, которые планируется использовать на финальном этапе расширения суперкомпьютера.

Лиза Спелман известна как горячий сторонник памяти Optane DC Persistent Memory. Она сыграла важную роль с процессорами Cascade Lake и Ice Lake, теперь с процессорами Sapphire Rapids анонсирована линейка PMem 300. И хотя она будет последней (Intel продала соответствующее подразделение), память все равно будет весьма полезна вместе с двумя поколениями CPU. Какие преимущества дает Optane DC Persistent Memory с нынешним поколением?

У памяти Optane DC Persistent Memory есть свои клиенты. Они смогут использовать ее с процессорами Sapphire Rapids и Emerald Rapids в том виде, который соответствует спецификациям Intel. На этом тема памяти для Intel будет закрыта.

Поддерживают ли процессоры Xeon Max с HBM2e память PMem 300? Поскольку иерархия памяти в таком случае расширилась бы еще на один уровень (кэши, HBM2e, DDR5 и PMem).

Нет, процессоры Xeon Max не поддерживают линейку PMem 300. Впрочем, это не означает, что память PMem не будет работать с контроллерами памяти Xeon Max CPU. Просто Intel не дает соответствующую валидацию.

Intel уже поставила несколько образцов процессоров Sapphire Rapids (до официального анонса 10 января), но Ice Lake и Cascade Lake по-прежнему составляют большую долю рынка. Можно ли ожидать и в будущем подобных плавных переходов с одного поколения на другое?

В будущем подобные переходы мы увидим неоднократно, что связано хотя бы с большими объемами CPU, используемыми нашими крупными клиентами. Скажутся и короткие продуктовые циклы при переходе на процессоры Emerald Rapids (2023) и Granite Rapids (2024). Партнеры Intel, такие как IONOS с Bare Metal Server, подтверждают данную точку зрения.

На этом мы заканчиваем с информацией, полученной в интервью с Лизой Спелман. Но Intel предоставила дополнительные подробности, которыми мы поделимся ниже.

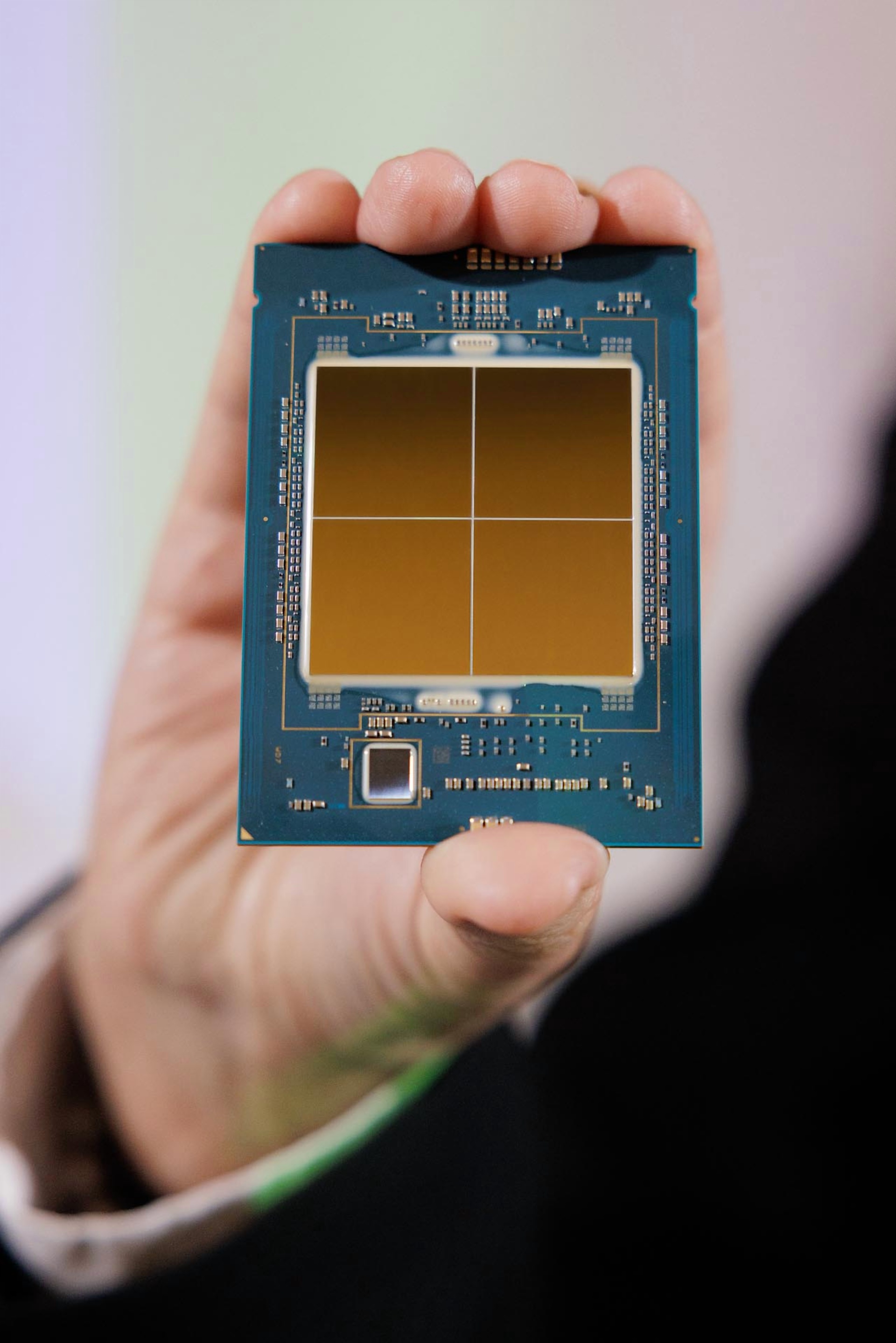

Подробности Sapphire Rapids

На сессии вопросов и ответов нам удалось получить дополнительные подробности Sapphire Rapids. Сначала стоит поговорить об интеграции ускорителей на аппаратном уровне. Блоки QAT, IAA, DSA и DLB встроены в mesh-интерконнект в виде комплекса ускорителей. Для приложений они видны как ускорители PCI Express и CXL. Но для доступа требуются драйверы на уровне ядра.

Ядра CPU и ускорители имеют доступ к кэшу последнего уровня LLC и контроллерам памяти всех тайлов – в случае процессоров Sapphire Rapid с четырьмя тайлами.

Кроме того, Intel раскрыла подробности пропускной способности памяти и задержек. Переход с DDR4-3200 на DDR5-4800 обещает 50% прирост пропускной способности памяти – по крайней мере, в теории. Тесты чтения и Stream Triad показывают увеличение на пропускной способности на 45% с небольшим увеличением задержек. Если у серверных систем с памятью DDR4 наблюдаются задержки от 70 до 100 нс при средней нагрузке, то Sapphire Rapids и DDR5 изначально показывают около 100 нс.

Но с таким увеличением задержек можно смириться, тем более режим Default Page Mode был переведен на Closed Page для увеличения производительности, пусть и с негативными последствиями для задержек в режиме бездействия, которые стали на 12-17 нс выше. Влияние памяти DDR5 само по себе оценивается в 7-12 нс. AMD с последними процессорами EPYC пришла к таким же выводам.

Если посмотреть на отдельные модели Sapphire Rapids, то они довольно сильно разделяются по базовой частоте и Boost. С наборами инструкций AVX2 и AVX-512, а также SSE, мы получаем уже три уровня частоты Xeon. В случае Sapphire Rapids добавляется еще четвертый уровень, при использовании AMX выставляется базовая частота (AMX P1), частоты All-Core Turbo (AMX P0n) и Half-Core Turbo (AMX P0half).

Частоты Turbo еще более тесно связаны с используемыми наборами инструкций, чем раньше. Причем статического отношения между ISA и частотами Turbo нет. Если не все ядра загружены сложными вычислениями AVX 512 и AMX, процессоры Sapphire Rapids могут показывать высокие тактовые частоты на других ядрах, что также возможно с SSE/AVX2.

Intel для процессоров Sapphire Rapids ускорила переключение между разными уровнями частоты. Если Ice Lake требовалось около 20 мкс для переключения между SSE/AVX2 и AVX-512/AMX, теперь задержка уменьшена до всего одной микросекунды. В противоположном направлении переключение с AVX-512/AMX на SSE/AVX2 на Sapphire Rapids выполняется от 2 до 20 мкс, тоже намного быстрее. Что должно положительно сказаться на производительности и эффективности.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).