13 июня AMD проведет мероприятие "AMD Data Center and AI Technology Premiere", посвященное дата-центрам, на котором анонсирует новые серверные продукты. Ожидается, что AMD представит процессор EPYC с кодовым названием Bergamo, который оптимизирован для облачных вычислений, также мы наверняка получим подробности ускорителя MI300A.

13 июня AMD проведет мероприятие "AMD Data Center and AI Technology Premiere", посвященное дата-центрам, на котором анонсирует новые серверные продукты. Ожидается, что AMD представит процессор EPYC с кодовым названием Bergamo, который оптимизирован для облачных вычислений, также мы наверняка получим подробности ускорителя MI300A.

Дилан Патель и Джеральд Вонг уже опубликовали на Semianalysis.com анализ того, что AMD представит в виде архитектуры Zen 4c. Ранее AMD для каждого поколения процессоров использовала одинаковую архитектуру, причем это касалось даже разных линеек Ryzen и EPYC. AMD не вносила изменения в виде разных емкостей кэшей или отключения функциональных блоков, как любит делать Intel. Но в случае Zen 4c были внесены многочисленные изменения, которые, в первую очередь, позволили AMD уместить до 128 ядер в корпусировке SP5.

То есть AMD уже пошла на шаг, который Intel планирует сделать с процессорами Sierra Forest в 2024 году. Напомним, что серверный процессор на маленьких экономичных ядрах позволит существенно увеличить свою эффективность.

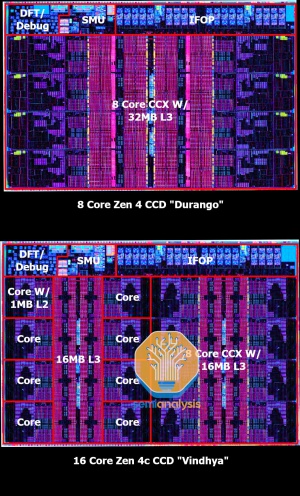

AMD с дизайном Bergamo нацелилась на удвоение ядер на кристалле Core Complex Die (CCD). Однако площадь чипа при этом отнюдь не удваивается. AMD смогла удвоить число ядер с 5-нм техпроцессом, при этом площадь CCD увеличилась лишь на 10%.

Причина кроется в урезании в два раза кэша L3 на кристалле Core Complex (CCX). То есть сейчас емкость составляет всего 16 Мбайт. Вместо одного CCX с восемью ядрами, как в случае обычных процессоров Zen 4, теперь на кристалле работают два CCX с восемью ядрами каждый, но уже на Zen 4c. Кэши L1 и L2 не изменились: 32 кбайт (инструкции и данные) и 1 Мбайт. Кэш L3 на CCD составляет прежние 32 Мбайт, но в расчете на ядро его уже в два раза меньше.

Чтобы сэкономить место, AMD отказалась от сквозных проводников TSVs. Они располагались на Zen 4 CCD в области кэша L3 (передача данных) и кэша L2 (питание/управление). То есть процессоры Bergamo с кэшем 3D V-cache не выйдут – AMD попросту не предусмотрела для него место.

Меньшие частоты экономят место и транзисторы

Процессоры EPYC с ядрами Zen 4c работают с меньшей базовой частотой, также и высоких частот Boost ожидать не стоит. Здесь кроется еще одна мера по экономии пространства. В конце концов, для дизайнов с высокими частотами требуется больше транзисторов, а также менее плотно заполненные ячейки, которые занимают больше места. Эффективность новых процессоров будет выше, поскольку можно энергопотребление снижается.

Проводники, которые идут из точки A в B на чипе, можно сделать длиннее. Что упрощает дизайн, блоки не нужно располагать на близком расстоянии друг от друга, ограничений при планировке чипа гораздо меньше.

AMD также использовала опыт, накопленный при разработке процессоров Zen 4. Ядро состоит из нескольких функциональных блоков (блок вычислений с плавающей точкой, блок целочисленных ветвлений, блок предсказания ветвлений, блоки чтения/записи, блоки кэшей разного уровня, блоки кэшей микроопераций, блоки декодирования и т.д.), которые разрабатываются отдельно, после чего собираются вместе. Такой подход не позволяет идеально использовать пространство, поскольку прямоугольные блоки разного размера собираются на одной площади, остаются неиспользованные зоны. В самих блоках тоже оставлено резервное пространство на тот случай, если что-то в дизайне придется менять.

Поскольку дизайн Zen 4 уже «обкатан», резервное пространство можно убрать. Поэтому и блоки проще комбинировать друг с другом. Соответственно, площадь ядра уменьшается.

Как обычно, дизайн чипа стал результатом сотрудничества между AMD и контрактным производителем TSMC. Только так AMD смогла перейти на дизайн чиплетов и новую технологию корпусировки. AMD для Bergamo использует новые ячейки 6T SRAM вместо 8T ранее. Что экономит порядка четверти транзисторов, а также и площадь на каждый бит SRAM. Вместо четырех линий к ячейкам подводятся только две, что тоже уменьшает занимаемое место. Вместо двухпортовых ячеек SRAM, которые могли писать и читать данные одновременно, теперь используется SRAM с записью и чтением на подъеме и спаде тактового импульса.

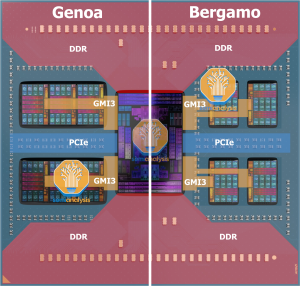

Восемь CCD и 128 ядер

Вместе с хорошо известным кристаллом IOD, благодаря которому платформа совместима с SP5, AMD установила в корпус процессора восемь CCD с 16 ядрами каждый. В итоге мы получаем 128 ядер, что и предложат процессоры EPYC в дизайне Bergamo. Число линий PCI Express (128x PCIe 5.0) и 12 каналов памяти (12x DDR5-4800) не изменились.

Финальные спецификации процессоров EPYC наверняка будут объявлены 13 июня. Пока что приведенные выше сведения носят неофициальный характер, хотя источник обычно хорошо осведомлен.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).