На конференции Hot Chips 28 AMD представила новые подробности об архитектуре Zen, в том числе и в тех областях, которые ранее не упоминались.

На конференции Hot Chips 28 AMD представила новые подробности об архитектуре Zen, в том числе и в тех областях, которые ранее не упоминались.

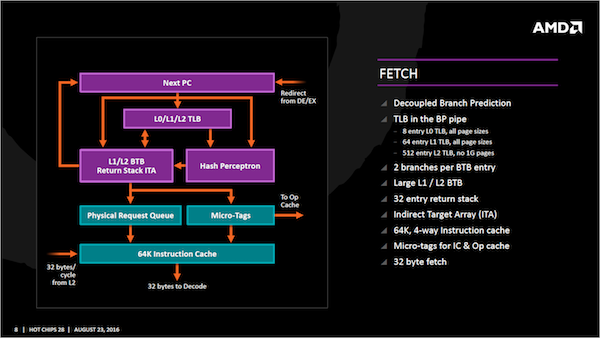

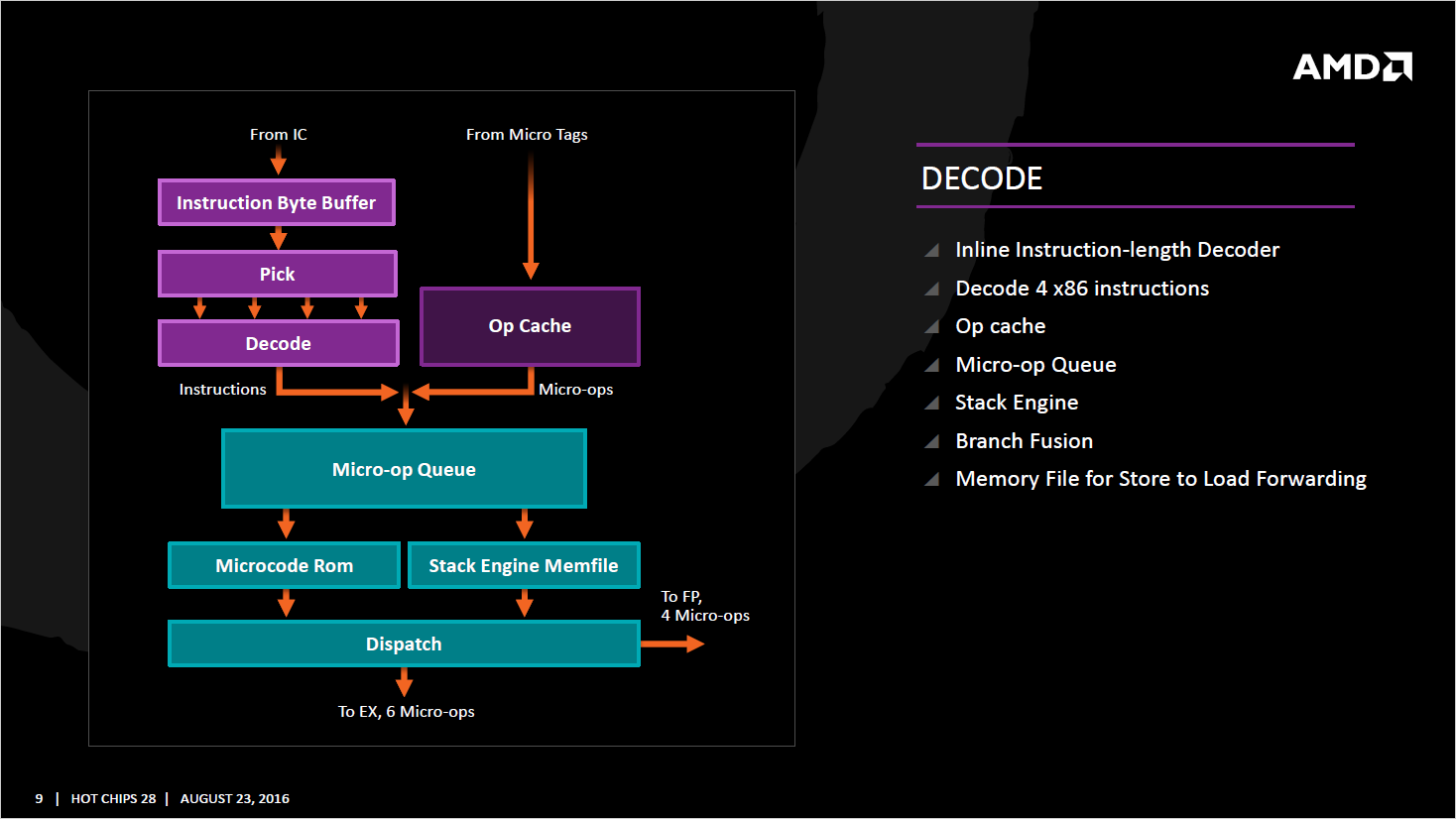

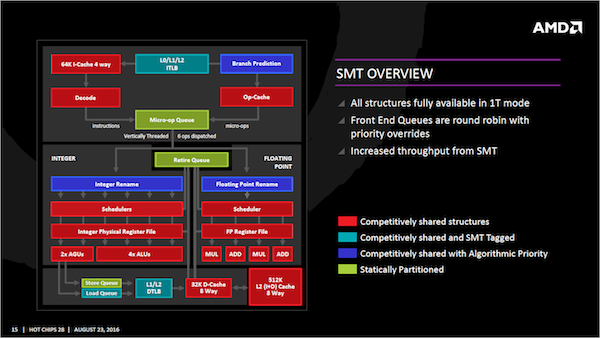

Первая область – кэш микроопераций, представляющий важную инновацию в архитектуре Zen. В кэше хранится уже декодированный код. Команды из декодеров или кэша микроопераций затем передаются в очередь микроопераций. К сожалению, AMD не раскрыла объем кэша микроопераций и очереди. В очереди, скорее всего, как и у Intel, идет анализ циклов. Если циклы будут найдены, то можно избежать обращения к фронтальной части конвейера.

Презентация архитектуры Zen на Hot Chips 28

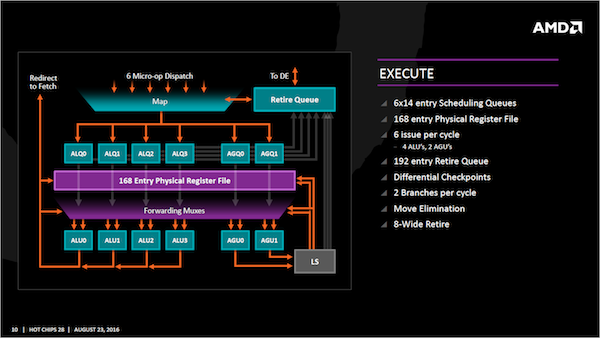

После диспетчера у Zen, в лучших традициях старых архитектур K8/K10, инструкции с целыми числами и с числами с плавающей запятой разделяются, у Intel же они поступают в общий Reorder Buffer. За такт диспетчер Zen может распределять 6 микроопераций с целыми числами. Что касается операций с плавающей запятой, то здесь за такт могут распределяться 4 микрооперации. Доступно 168 регистров для целых чисел и 160 для чисел с плавающей запятой.

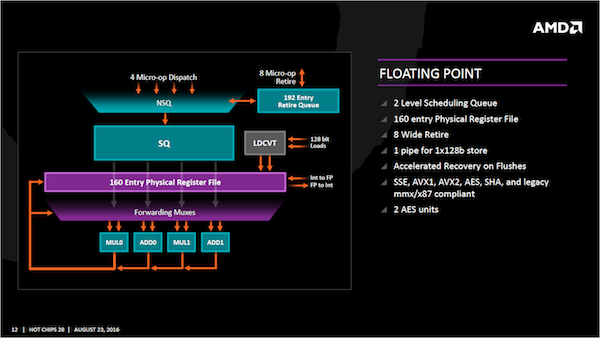

Вычисления с плавающей запятой выполняются двумя блоками 128-bit FP-MUL и двумя блоками FP-ADD. При необходимости, они могут объединяться в 256-bit AVX2. Пока нет информации о том, может ли AMD выполнять операции Fused Multiply Add (FMA) за такт. Intel использовала два подобных блока в Haswell. Если таких блоков у AMD нет, то Zen ближе к поколению Sandy Bridge, нежели Haswell.

Презентация архитектуры Zen на Hot Chips 28

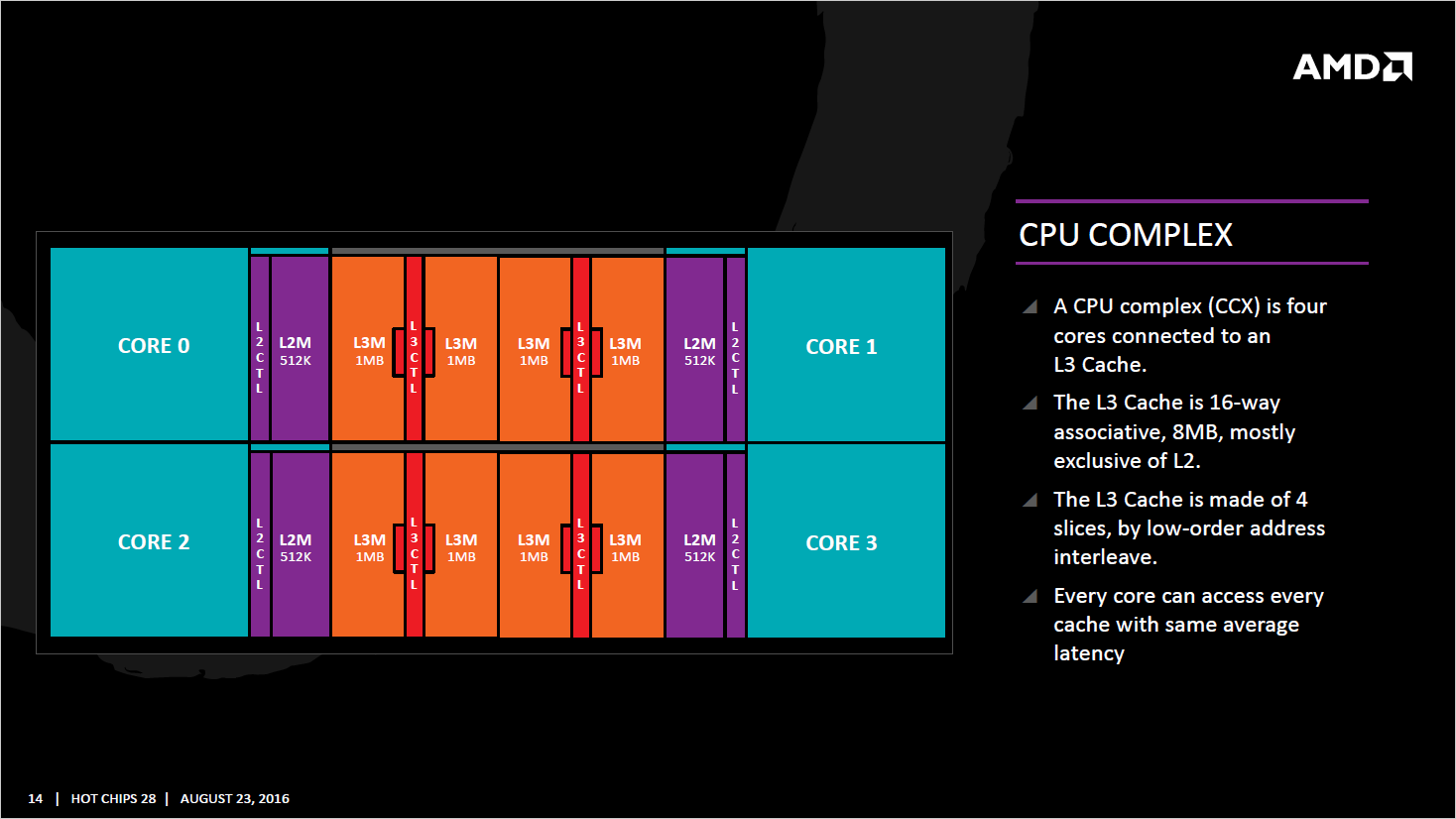

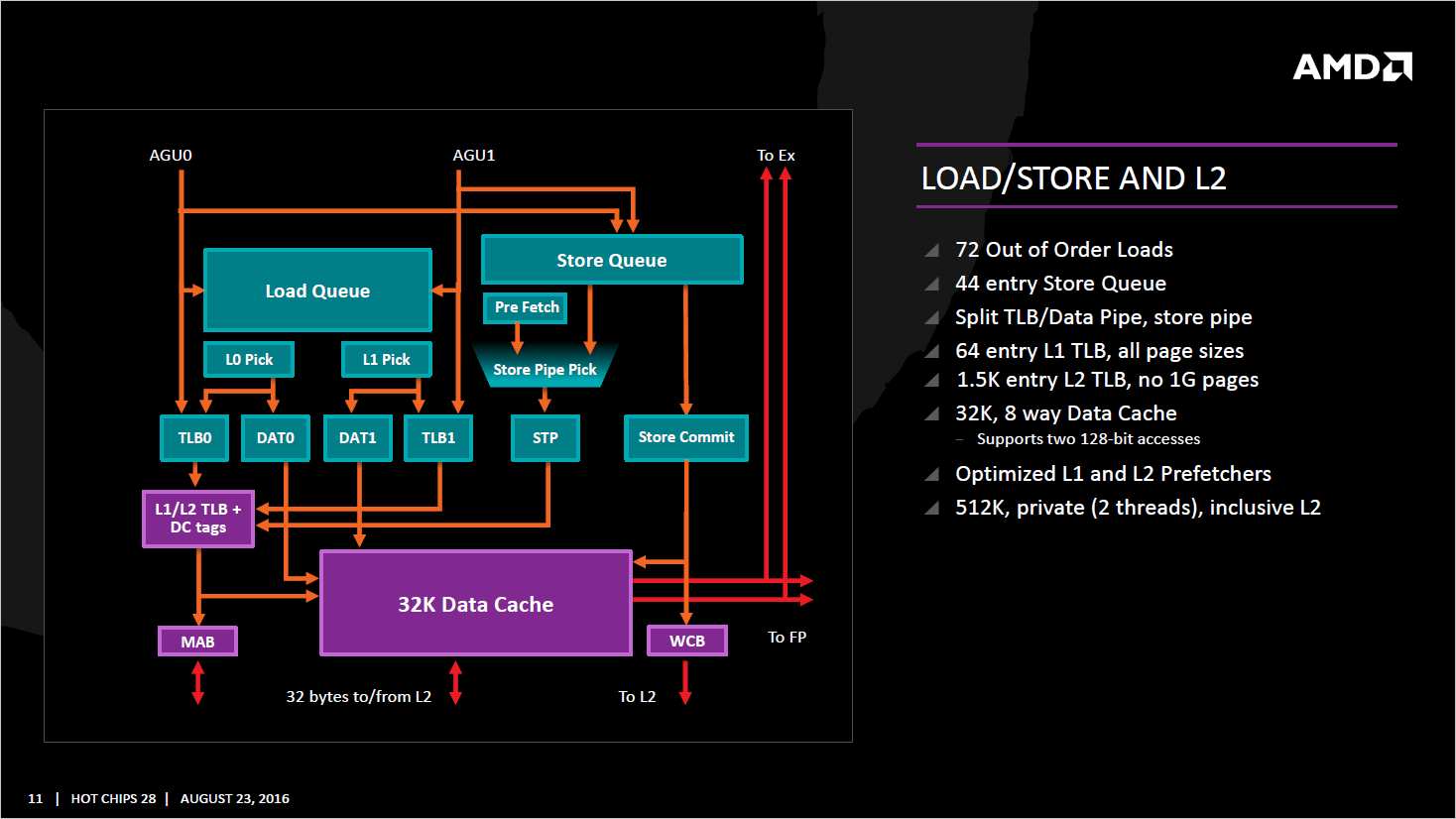

AMD ранее раскрыла часть подробностей о кэшах, теперь была дана более детальная информация. Кэш L1 составляет 96 кбайт, из которых 64 кбайт выделено на инструкции, а 32 кбайт – на данные. По крайней мере, для инструкций мы получаем в два раза больший кэш, чем у Skylake, для данных размер идентичен. Кэш L2 в два раза больше – 512 кбайт. Но важен не только размер, но и скорость работы кэшей. По сравнению с Bulldozer кэши L1 и L2 работают примерно в два раза быстрее, кэш L3 ускорился до пяти раз.

Презентация архитектуры Zen на Hot Chips 28

Чтобы упростить структуру процессоров, AMD объявила новый компонент: CPU Complex. CPU Complex состоит из четырех ядер вместе с кэшами L1 и L2, а также с двумя сегментами кэша L3 по 1 Мбайт на ядро. В результате мы получаем 8 Мбайт кэша L3 в CPU Complex. Чип Zeppelin, судя по слухам, будет содержать два таких CPU Complex, кроме CPU на нем будут присутствовать два канала памяти DDR4 и 32 линии PCI Express. Официально AMD пока не рассказала о части Uncore в архитектуре Zen.

Презентация архитектуры Zen на Hot Chips 28

CPU Naples, который тоже был показан параллельно с IDF, содержит 32 ядра, то есть четыре Zeppelin. Связь между четырьмя блоками Zeppelin выполняется через Hyper-Transport. Соответственно, будут доступны 128 линий PCI Express и восемь каналов памяти DDR4. Чип будет устанавливаться в сокет с более чем 5.000 контактами.

Впрочем, данную информацию AMD пока не подтверждает. Позднее должны появиться сведения об отдельных моделях, частотах и количестве ядер.