Исследователи Google AI, а именно команда Brain Team, представила технологию Chip Design with Deep Reinforcement Learning, то есть дизайн чипов с использованием глубокого обучения. Современные архитектуры чипов разрабатываются годами. В зависимости от размера и сложности проекта, на разработку уходит от двух до пяти лет.

Исследователи Google AI, а именно команда Brain Team, представила технологию Chip Design with Deep Reinforcement Learning, то есть дизайн чипов с использованием глубокого обучения. Современные архитектуры чипов разрабатываются годами. В зависимости от размера и сложности проекта, на разработку уходит от двух до пяти лет.

И довольно сложно предсказать, какие именно требования к дизайну чипов будут актуальны через два-пять лет. Уменьшение циклов дизайна - важная тема в микроэлектронике, поскольку в таком случае можно более эффективно ориентировать дизайн чипа под новые требования.

Планирование структуры чипа (Floorplanning на английском) - важный этап разработки, отнимающий немало времени. Чип, будь то процессор, GPU или любая другая микросхема, состоит из десятков функциональных блоков. Например, вычислительные ядра процессоров, различные кэши, контроллеры памяти, контроллеры интерфейсов и т.д. Все блоки должны соединяться с теми или иными другими блоками, и эти соединения нельзя проводить как попало.

Несмотря на существенную долю автоматизации при дизайне современных чипов, инженеры все равно тратят на планирование чипа недели и месяцы, чтобы найти оптимальную раскладку. Проблема в том, что граф netlist может содержать миллионы связей. Причем получившуюся раскладку еще необходимо оптимизировать по энергопотреблению, производительности и занимаемой площади (PPA), что тоже требует немало времени.

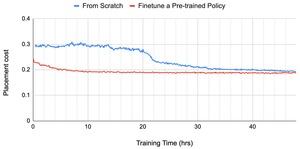

Технология Chip Design with Deep Reinforcement Learning как раз призвана автоматизировать расположение блоков и прокладку связей. Для этой цели используется особая сеть глубокого обучения Graph Neural Network. Все подробности приведены в блоге Google.

В нейросеть можно загружать различные требования, например, чтобы блоки с интерфейсами располагались на периферии чипа. Также есть и другие спецификации, чтобы максимально сократить длину соединений и избежать пересечений.

На иллюстрации показано расположение блоков Ariane, процессора RISC-V с открытым исходным кодом, который использовался в качестве примера тренировки.

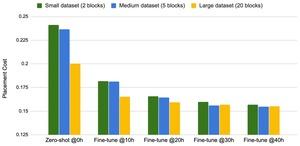

Как показали первые симуляции, чем более сложной была структура графа netlist, тем лучшие результаты обеспечивала нейросеть.

Google AI на данный момент тренирует систему на разных чипах. Но уже ясно, что технология Chip Design with Deep Reinforcement Learning может быть адаптирована под разные требования. Конечно, Google нацеливается, в первую очередь, на разработку собственных ускорителей. Новый метод появился слишком поздно, чтобы использоваться в первой SoC Google для смартфонов. Да и предыдущие вычислительные ускорители TPU разрабатывались классическим способом.

Но Google видит в Chip Design with Deep Reinforcement Learning возможность существенно сократить цикл разработки чипов. Поэтому новые чипы будут появляться намного быстрее.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).