На прошлой неделе в рамках конференции Linley Spring Processor Conference 2021 компания Cerebras представила второе поколение Wafer Scale Engine с 850.000 ядрами ИИ. SiFive также объявила о расширении Intelligence IP, добавив новые ядра X280. Они опираются на ядра U7 Series с RISC-V ISA.

На прошлой неделе в рамках конференции Linley Spring Processor Conference 2021 компания Cerebras представила второе поколение Wafer Scale Engine с 850.000 ядрами ИИ. SiFive также объявила о расширении Intelligence IP, добавив новые ядра X280. Они опираются на ядра U7 Series с RISC-V ISA.

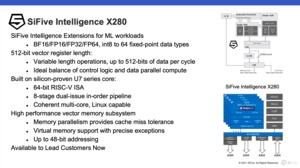

Intelligence X280 обеспечивает ускорение нагрузок ИИ и машинного обучения, начиная от INT8, BF16 и FP16, заканчивая FP32 и FP64. Решающим фактором являются 512-битные векторные регистры, которые позволяют вычислять 512-битный вектор за такт с 256-битный конвейером и 256-битным контроллером памяти. Скалярные арифметические блоки хорошо балансируются векторными. На ядрах может работать Linux.

Векторные расширения современных CPU становятся все более важными. ARM недавно представила новое расширение набора инструкций AArch64 вместе с Armv9 с поддержкой SVE и SVE2. Вычисление 512 бит за такт у Intelligence X280 открывает весьма широкие возможности. На диаграмме Intelligence X280 видна фронтальная часть конвейера, распределяющая данные на скалярные и векторные блоки, затем имеется блок Load/Store и кэш L2 с пропускной способностью 256 бит за такт.

Одним из первых покупателей Intelligence X280 станет канадский стартап Tenstorrent, к которому в январе присоединился Джим Келлер в качестве CTO.

"The Tenstorrent architecture addresses the growing demands that come with data-written code as part of Software 2.0," сказал Келлер. "We’re excited to partner with SiFive because of their ability to deliver CPUs and software for the modern RISC-V ecosystem."

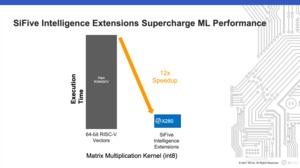

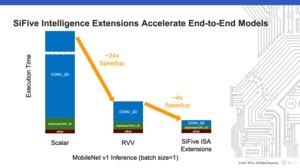

Intelligence X280 полностью совместим с RISC-V Vector Extension (RVV). По сравнению с ядрами RV64GCV, Intelligence X280 оказывается быстрее в 12 раз при выполнении 64-битных векторных вычислений. Есть еще одно сравнение, показывающее важность использования новых наборов инструкций: переход на расширения RVV по сравнению со скалярными ядрами дает прирост производительности 24x, а расширения SiFive ISA дают еще 4x прирост.

Пока ни Tenstorrent, ни SiFive не дают подробностей о структуре ядер и первых реализациях. Теоретически SoC может содержать большое количество данных ядер. В дата-центрах используются чипы, которые содержат большое количество ядер. Но Tenstorrent недавно высказалась насчет разработки дизайнов для периферийных и микро-периферийных сценариев, поэтому можно ожидать чипы с небольшим количеством ядер.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).