Страница 1: Четвертое поколение EPYC Genoa – атака AMD на серверном сегменте

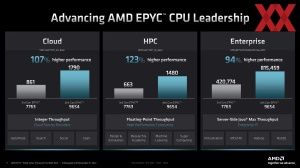

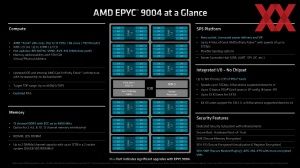

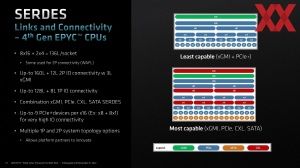

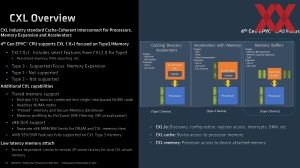

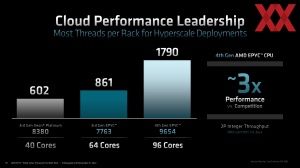

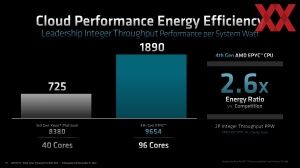

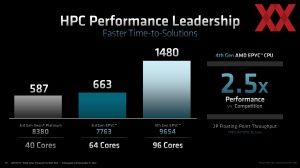

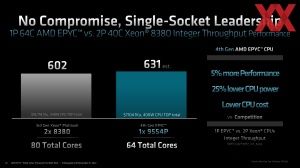

Под лозунгом "together we advance data centers" AMD представила четвертое поколение процессоров EPYC под кодовым названием Genoa. Оно выделяется, в первую очередь, использованием ядер Zen 4, поддержкой DDR5, PCI Express 5.0, CXL и другими возможностями ввода/вывода. AMD с четвертым поколением EPYC нацелилась на абсолютное доминирование во всех областях: облако (Cloud), высокопроизводительные вычисления (HPC), корпоративный сегмент (Enterprise) и оптимизированные серверы для разных нагрузках.

Под лозунгом "together we advance data centers" AMD представила четвертое поколение процессоров EPYC под кодовым названием Genoa. Оно выделяется, в первую очередь, использованием ядер Zen 4, поддержкой DDR5, PCI Express 5.0, CXL и другими возможностями ввода/вывода. AMD с четвертым поколением EPYC нацелилась на абсолютное доминирование во всех областях: облако (Cloud), высокопроизводительные вычисления (HPC), корпоративный сегмент (Enterprise) и оптимизированные серверы для разных нагрузках.

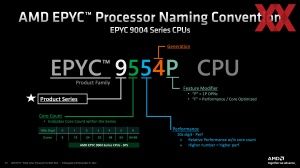

Но AMD пока что представила только процессоры на Zen 4 общего назначения, которые являются ключевым бизнесом AMD. Облачные версии под кодовым названием Bergamo с ядрами Zen 4c, Siena для телекоммуникаций и пограничных серверов (Edge) и Genoa-X для специальных технических решений выйдут чуть позже.

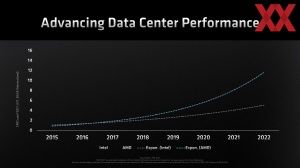

AMD вновь подтвердила, что пятое поколение под кодовым названием Torino выйдет в 2024 году. Кроме того, AMD подчеркивает тот факт, что компания последовательно вносит улучшения с каждым поколением и выпускает все вовремя, чем не может похвастаться Intel. И в будущем AMD продолжит следовать своим планам.

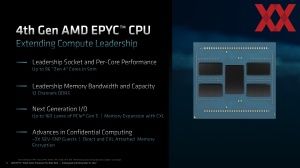

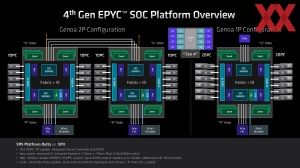

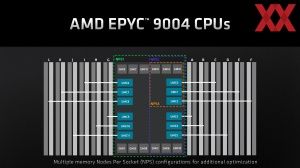

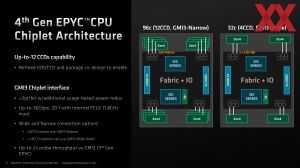

AMD ранее уже раскрыла наиболее важные спецификации Genoa EPYC, в том числе 96 ядер Zen 4, распределенных по 12 чиплетам CCD с восемью ядрами каждый. Они подключаются к центральному кристаллу IOD. Последний обеспечивает подключение памяти DDR5 и линий PCI Express 5.0.

AMD перешла на новый сокет SP5 из-за более крупной корпусировки, а также из-за расширенной подсистемы ввода/вывода с DDR5 и PCI Express 5.0. Процессор устанавливается в сокет LGA6096 с 6.096 контактами. Размер корпусировки процессоров EPYC составляет 72 x 75 мм, расстояние между контактами – матрица 0,94 x 0,81 мм. Напомним, что размер сокета SP3 был 58,5 x 75,4 мм.

AMD немного изменила механизм сокета, чтобы оптимизировать контактное давление. Подпружиненная крепежная рамка опускается, после чего фиксируется винтом. Причем непосредственно давление на сокет, то есть между контактными площадками и контактами LGA, прикладывается кулером. Он крепится к ILM шестью винтами, которые вкручиваются с заданным крутящим моментом.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).

Genoa и архитектура Zen 4

Одно из крупных преимуществ архитектуры чиплетов AMD заключается в том, что CCD процессоров Ryzen (Threadripper) и EPYC идентичны. AMD производит CCD по 5-нм техпроцессу на мощностях TSMC, восемь ядер Zen 4 дополняются 32 Мбайт кэшем L3 – как для процессоров Ryzen, так и EPYC. CCD имеет размер 70 мм², он содержит 6,5 млрд. транзисторов.

Архитектура Zen 4 у процессоров Ryzen и EPYC не отличается. AMD при разработке архитектуры учитывала оба направления. Раньше такой подход был вполне успешным, хотя Intel вносит оптимизации в производительные ядра, поэтому они различаются для Core и Xeon.

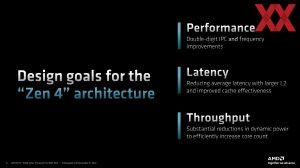

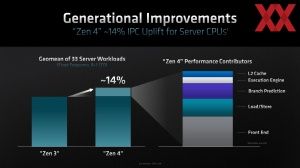

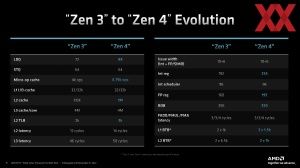

AMD указывает прирост IPC для процессоров Ryzen 13%, но для EPYC он увеличился до 14%. Разница появилась по причине того, что здесь берется среднее по нескольким приложений, и их набор для серверного сегмента различается. Задержки почти не увеличились, несмотря на большее число CCD. Причина кроется и в увеличении размера кэшей. Кэш L2 удвоился, но кэш L3 не изменился. Помимо чистой производительности, AMD фокусировалась и на повышении эффективности.

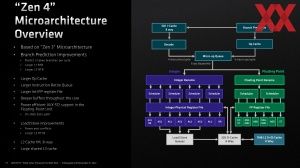

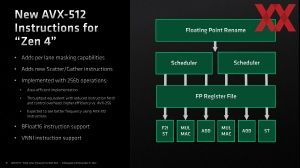

С архитектурой Zen 4 было пересмотрено предсказание ветвлений, которое теперь работает намного лучше. За такт выполняются два предсказания. Кэш микроопераций был увеличен на 68%, в очередь микроопераций он выдает девять micro-ops вместо восьми ранее. По функциональным блокам с целыми числами и плавающей запятой изменений нет, но регистровые файлы увеличились. Блоки с плавающей запятой теперь могут выполнять инструкции AVX-512.

В задней части конвейера улучшились блоки чтения/записи, очередь увеличилась на 22%. Были внесены оптимизации и в D-кэш, чтобы снизить число конфликтов при доступе к данным.

На слайдах показаны численные значения. Отметим более крупный кэш микроопераций, кэш L2, L2 TLB, целочисленный регистровый файл, регистровый файл с плавающей запятой, L2 и L2 BTB (выделен синим).

Но есть некоторые детали, по которым архитектура Zen 4 оказалась хуже Zen 3. Задержки L2 увеличились с 12 до 14 тактов, что не особо огорчает, учитывая в два раза больший кэш. Задержка L3 увеличилась с 46 тактов до 50.

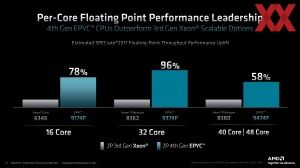

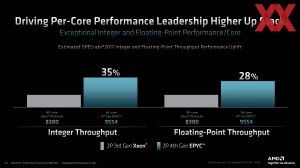

Важным преимуществом архитектуры EPYC и процессоров Zen 4 является поддержка AVX-512. В данном случае AMD преобразует 512-битную операцию в 256-битные. Как указывает AMD, частоты ядер при выполнении инструкций AVX-512 не снижаются, в отличие от процессоров Intel. По числу инструкций реализация AVX-512 от AMD идентична Cooper Lake/Ice Lake от Intel. Конечно, с поколением Sapphire Rapids Intel планирует расширить поддержку AVX-512 новыми инструкциями, но AMD указывает, что уже поддерживает самые важные.

Выполнение инструкций AVX-512 разделено на две 256-битные операции, которые выполняются одна за другой. Архитектура Zen 4 содержит четыре 256-битных исполнительных блока, два для чисел с плавающей запятой, два целочисленных.

Поскольку третье поколение EPYC не поддерживает инструкции AVX-512, то есть выполняет соответствующие вычисления существенно меньшей пропускной способностью, новое поколение здесь выходит вперед. Интересно будет провести сравнение с Intel.

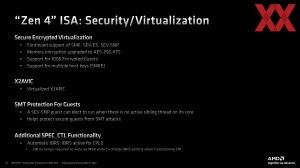

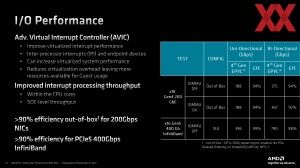

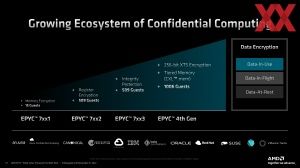

Безопасность и виртуализация очень важны в сегменте дата-центров. Здесь EPYC поддерживает различные функции, знакомые по предыдущим поколениям. На сокет поддерживаются 1.006 зашифрованных гостевых систем. Также поддерживается SMKE (multiple host keys).

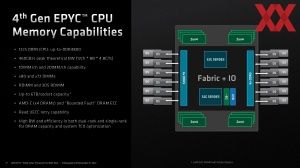

Genoa и DDR5

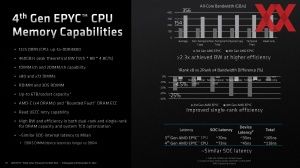

Genoa поддерживает 12 каналов памяти DDR5-4800 и 6 Тбайт на канал памяти, причем на каждый канал можно установить два DIMM. Пропускная способность памяти с 12 каналами составляет 460 Гбайт/с. Помимо обычных модулей RDIMM и 3DS RDIMM с 80-битной шиной (2x 40 бит, 2x 32 данных + 8 ECC), AMD поддерживает модули DDR5 с 72-битной шиной, то есть без ECC.

Предшественники Milan поддерживали лишь восемь каналов памяти DDR4-3200, то есть пропускная способность была ограничена 204,8 Гбайт/с. В случае Genoa теоретическая пропускная способность увеличилась до 460 Гбайт/с, на практике AMD говорит об удвоении пропускной способности. Разница в рангах DDR 1Rank x8 и 2Rank x4 не так велика, можно использовать менее дорогую память 2Rank x4 без серьезного падения производительности.

Что касается доступа к памяти, то новый IOD с DDR5 привел к изменению задержек.

| | Задержка SoC | Задержка модуля | Итого |

| 3. поколение EPYC (Milan) | ≈ 70 нс | ≈ 35 нс | ≈ 105 нс |

| 4. поколение EPYC (Genoa) | ≈ 73 нс | ≈ 45 нс | ≈ 118 нс |

В случае IOD, то есть контроллера памяти, AMD смогла получить почти идентичные задержки (73 против 70 нс). У модулей DDR5 задержка чуть выше – 10 нс из-за дизайна (частоты, тайминги и т.д.), что обуславливает отличия по суммарной задержке. Но с учетом продолжающегося совершенствования памяти DDR5, AMD ожидает намного меньших задержек в будущем, чем с Genoa на данный момент.

Поддерживаются конфигурации NUMA NPS1, NPS2 и NPS4. Использование NPS2 и NPS4 действительно имеет смысл в некоторых случаях, поскольку ограничивает выполнение приложения только на определенной области CCD и каналах памяти.

Производители материнских плат и серверов могут выбирать между установкой всех 24 слотов DIMM или только 12, чтобы обеспечить один модуль на канал. Чередование памяти позволяет установить только два, четыре, шесть, восемь или десять слотов DIMM, что имеет смысл только в том случае, если приложение не чувствительно к объему и пропускной способности памяти. Но в случае облачных провайдеров, например, такой шаг позволит сэкономить.