Страница 2: Архитектура RDNA 3 и дизайн чиплетов

До сих пор подробности архитектуры RDNA 3 не раскрывались. Но сейчас мы можем устранить этот недостаток, поэтому ниже мы поговорим об архитектуре новых видеокарт.

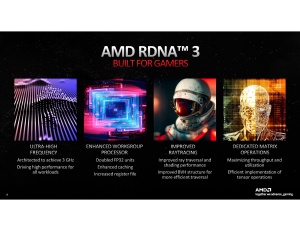

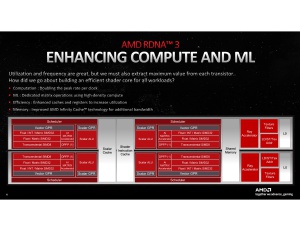

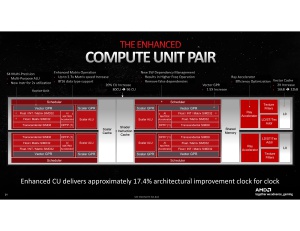

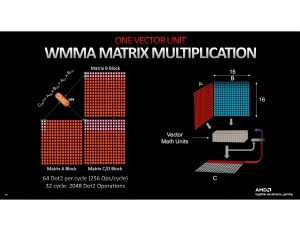

Начнем с самого маленького элемента архитектуры: вычислительные блоки Compute Unit (CU). AMD уже некоторое время использует сдвоенные CU. Каждый блок CU содержит два диспетчера, которые отвечают за распределение вычислительных операций, один векторный и один целочисленный исполнительные блоки.

Векторные исполнительные блоки могут выполнять вычисления с плавающей запятой точностью до 32 бит (FP32). Кроме исполнительных блоков, в составе CU есть ускоритель трассировки лучей, матричный ускоритель, блоки чтения/записи, а также кэш L0. Объем кэша L0 составляет 32 кбайт на пару CU, то есть в два раза больше, чем в архитектуре RDNA 2.

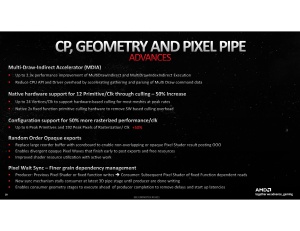

Кроме того, AMD встроила ускоритель Multi-Draw-Indirect-Accelerator (MDIA), который работает с примитивами (самыми маленькими элементами, из которых состоит сцена). В результате удалось увеличить производительность геометрических и пиксельных вычислений на 50-100%.

Производительность IPC RDNA 3 CU выросла на 17,4% по сравнению с RDNA 2 CU.

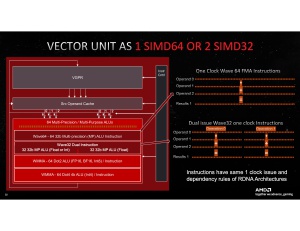

Важное изменение архитектуры RDNA 3 коснулось процессоров WGP (Workgroup Processors), которые представляют собой пары CU. Блоки FP32 теперь поддерживают "Dual Issue", то есть выполняют две вычислительных инструкции вместо одной. Но инструкции должны быть идентичны, что часто бывает, когда GPU используется для вычислений. Чтобы максимально раскрывать потенциал параллельного выполнения на уровне инструкций ILP (Instruction Level Parallelism), подача инструкций (wavefront) должна быть ориентирована на параллельное выполнение. И в идеальном случае вычислительный блок CU (compute unit) сможет выполнять 128 вычислительных инструкций FP32 вместо 64 ранее.

Параллелизм на уровне инструкций ILP – сравнительно простой способ увеличения вычислительной производительности. Но здесь многое зависит от возможности дублирования вычислительных инструкций, поскольку только так можно выполнить две инструкции на одном блоке. Интересно, насколько велико будет увеличение ILP на практике. У AMD наверняка есть собственные расчеты, но компания пока ими не поделилась.

AMD увеличила регистры VGPR (Vector General-Purpose Registers) на 50%, чтобы более эффективно нагружать вычислительные блоки CU. Каждый блок CU содержит два выделенных ускорителя искусственного интеллекта AI, которые могут быстрее выполнять простые вычисления INT8 и BFLOAT16. Вряд ли эти блоки AI стоит напрямую сравнивать с ядрами Tensor, но AMD заявляет об увеличении соответствующей производительности в 2,7 раза. На данный момент технология FSR не опирается на искусственный интеллект, но все может измениться в будущем. Между тем в профессиональном сегменте появляются приложения, которые умеют использовать блоки AI.

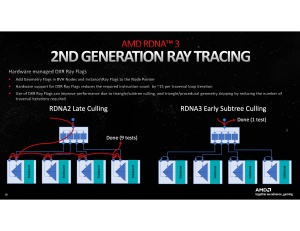

Улучшения производительности трассировки лучей связаны с тем, что соответствующие блоки могут рассчитывать на 50% больше лучей на такт. Структура дерева BVH для каждой операции трассировки луча по-прежнему просчитывается на потоковых процессорах. А блоки RT ускоряют, главным образом, операции Ray Box Sorting и Ray Traversal.

Вся иерархия кэшей была пересмотрена. Мы уже упомянули на 50% увеличившийся кэш L0, но также и кэш L1 стал в два раза больше, чем в архитектуре RNDA 2. Теперь емкость составляет 256 кбайт на WGP, в сумме она увеличилась до 3 Мбайт, подключение тоже на 50% быстрее – 6.144 бит/такт.

50% увеличение емкости коснулось и кэша L2, который достиг 6 Мбайт. Более важным является то, что интерфейс с Infinity Cache ускорился в 2,25x раза до 2.304 бит/такт. Разве что емкость кэша Infinity Cache уменьшилась со 128 до 96 Мбайт, но более скоростное подключение нивелирует этот недостаток.

Наконец, интерфейс памяти тоже ускорился. 384-битный интерфейс работает на 50% быстрее – 960 Гбайт/с. Но система кэширования здесь даже важнее: если данные чаще будут оставаться в пределах кэшей L0-L2, а также Infinity Cache, то обращения к памяти GDDR6 будут выполняться реже.

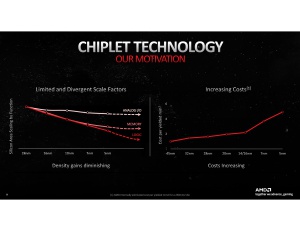

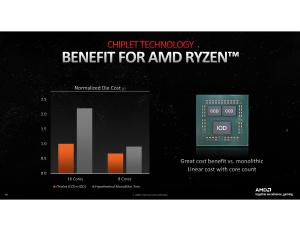

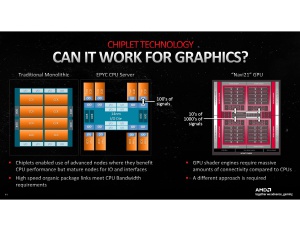

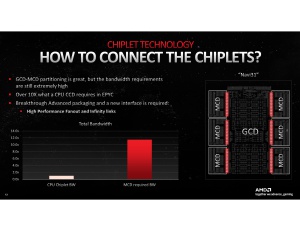

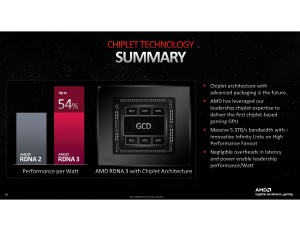

Дизайн чиплетов

Еще одной отличительной особенностью Navi 3x GPU на архитектуре RDNA 3 является дизайн чиплетов. AMD впервые перешла на него со своими игровыми GPU. В сегменте CPU дизайн чиплетов был весьма успешен, но в случае GPU требования по пропускной способности интерконнекта уже другие, поэтому переход не так прост.

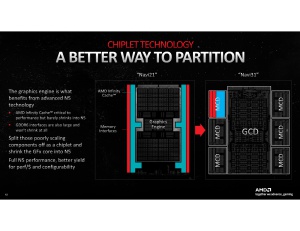

Для соединения CCD и центрального IOD AMD использовала Infinity Fabric. Физически интерконнект представляет собой несколько сотен контактов между CCD и IOD. Но в случае GPU требуется более высокая пропускная способность, особенно для соединения между GCD и MCD. Что потребовало больше соединений, у Navi 3x GPU речь идет десятках тысяч соединений между MCD и GCD.

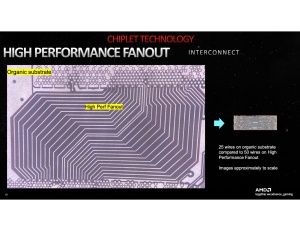

Классический способ с органической подложкой уже недостаточен для прокладки десятков тысяч соединений между кристаллами. Здесь пригодилась совместная разработка AMD и TSMC под названием 2.5D Elevated Fanout Bridge (EFB). AMD уже использовала эту технологию с ускорителями Radeon Instinct MI200.

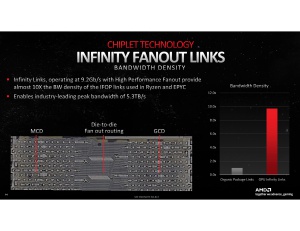

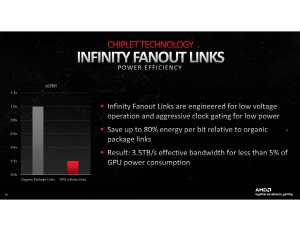

AMD удалось достичь пропускной способности 9,2 Гбит/с через EFB, в сумме по всем Infinity Link она составила 5,3 Тбайт/с. Если сравнивать с другими методами интерконнекта, EFB работает очень эффективно, то есть AMD удалось получить низкое энергопотребление.

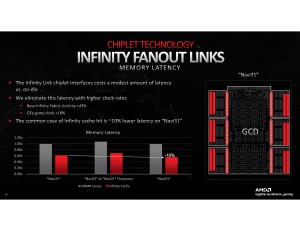

Но у дизайна чиплетов есть свои недостатки, известные по процессорам Ryzen и EPYC. При передаче данных между разными чиплетами увеличиваются задержки. В случае Navi 3x GPU кэш Infinity Cache и контроллеры памяти располагаются в MCD, которые подключаются к GCD.

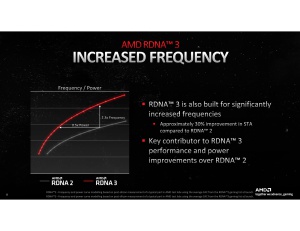

Но благодаря увеличению частоты Infinity Fabric и GPU, AMD удалось снизить задержки памяти на 10% по сравнению с Navi 21.

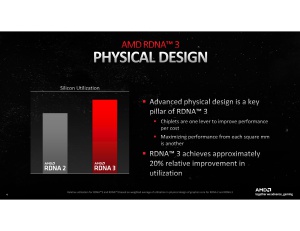

В корпусировке установлен центральный кристалл Graphics Chiplet Die (GCD) и несколько кристаллов памяти Memory Chiplet Dies (MCD). GCD производится по 5-нм техпроцессу на мощностях TSMC, а MCD – по 6-нм, тоже на TSMC. Если верить AMD, дизайн на основе чиплетов улучшает гибкость. Можно сравнительно легко выпустить большое количество маленьких идентичных кристаллов MCD, которые будут комбинироваться с центральным кристаллом GCD в требуемом количестве. Сам GCD может быть в разных стадиях расширения. Площадь GCD составляет 300 мм², а MCD – всего 37,5 мм² для каждого.

Один кристалл GCD и шесть MCD в составе Navi-31 GPU на Radeon RX 7900 XTX дают вместе 58 млрд. транзисторов на суммарной площади 525 мм² (300 мм² + 6x 37,5 мм²). AD102 GPU на видеокарте GeForce RTX 4090 содержит 76 млрд. транзисторов на площади 608,3 мм². NVIDIA опирается на монолитный кристалл, который производится на мощностях TSMC по техпроцессу 4 нм.