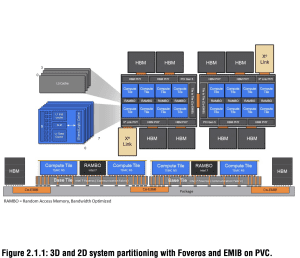

HPC-ускоритель Ponte Vecchio (PVC) можно назвать самым сложным полупроводниковым чипом за последние годы. Он будет содержать 47 активных тайлов, которые соединяются в одной корпусировке через мосты Co-EMIB и Foveros, в общей сложности будут использоваться пять разных техпроцессов.

HPC-ускоритель Ponte Vecchio (PVC) можно назвать самым сложным полупроводниковым чипом за последние годы. Он будет содержать 47 активных тайлов, которые соединяются в одной корпусировке через мосты Co-EMIB и Foveros, в общей сложности будут использоваться пять разных техпроцессов.

Многие подробности Ponte Vecchio были известны и ранее. Но на ISSCC 2022 Intel упомянула различные интересные детали о производстве подобного чипа и конструкции корпусировки.

У представленной ранее конфигурации Ponte Vecchio были задействованы 16 вычислительных тайлов, которые производятся TSMC по техпроцессу N5. Восемь тайлов памяти (RAMBO) представляют собой чипы SRAM по техпроцессу Intel 7 (10 nm). Кроме того, имеются восемь чипов памяти HBM2E (сторонний производитель), а две крупные подложки Foveros Base Tile производятся по техпроцессу Intel 7. Для двух тайлов Intel Xe-Link используется техпроцесс TSMC N7.

| Количество | Техпроцесс | |

| Вычислительный тайл Compute Tile |

16 | TSMC N5 |

| RAMBO Cache | 8 | Intel 7 |

| Базовые тайлы Foveros Base Tiles |

2 | Intel 7 |

| Xe-Link Tile | 2 | TSMC N7 |

| HBM2E | 8 | - |

| EMIB | 11 | - |

| Итого | 47 | |

| Дополнительные термальные тайлы | 16 | |

| В сумме | 63 |

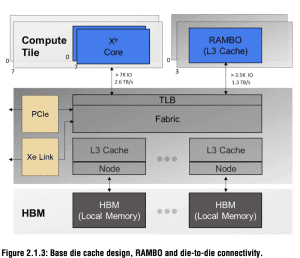

Летом 2021 года мы уже рассматривали структуру вычислительных тайлов. Но вот информация о кэше RAMBO новая. Данный кэш SRAM состоит из четырех банков емкостью 3,75 Мбайт каждый, что дает 15 Мбайт на тайл. С четырьмя тайлами RAMBO на каждом из двух базовых тайлов мы получаем 120 Мбайт дополнительного кэша. Он подключен с пропускной способностью 1,3 Тбайт/с на тайл. Кстати, вычислительные тайлы подключены на 2,6 Тбайт/с.

Базовый тайл имеет площадь 646 мм², он обеспечивает необходимую инфраструктуру для PvC. В том числе контроллеры памяти, компоненты питания Fully Integrated Voltage Regulators (FIVR), систему управления питанием и 16 линий host-интерфейса PCIe 5.0 или CXL. Базовый тайл состоит из 17 слоев и производится по техпроцессу Intel 7.

47 активных тайлов имеют общую площадь 2.330 мм². Если учитывать дополнительные термальные тайлы, площадь составит 3.100 мм². Непосредственно корпусировка имеет размер 77,5 x 62,5 мм (4.844 мм²). Ускоритель Ponte Vecchio выполнен в модуле OAM и подключается к host-системе по 4.468 контактам.

Вычислительные тайлы и кристаллы RAMBO-кэша располагаются на базовом тайле в непосредственной близости. С подложкой они соединяются через шариковые контакты с расстоянием всего 36 мкм. Для соединения базовых тайлов используется технология Co-EMIB, расстояние между шариковыми контактами составляет уже 55 мкм. То же самое касается чипов HBM2E. Базовые тайлы подают питание на вычислительные кристаллы и RAMBO-кристаллы через специальные сквозные проводники TSV в различных конфигурациях, а для распределения питания используются толстые металлические слои.

Еще один компонент базового тайла - 144 Мбайт кэша L3 в каждом, а также соединения Memory Fabric (MF) со сложной геометрической топологией с пропускной способностью 4.096 байт на такт. Банки памяти расположены под вычислительными тайлами, они представляют собой расширение кэшей L1 и L2. У последних двунаправленная пропускная способность составляет 64 байт на такт.

Для соединения вычислительных тайлов и кристаллов RAMBO используется Foveros Die Interconnect (FDI). Каждый канал FDI разделен на восемь групп, каждая группа состоит из 800 линий для вычислительных кристаллов. Эффективность энергопотребления FDI составляет 0,2 pJ/B. Один интерфейс обеспечивает 2,8 GT/s.

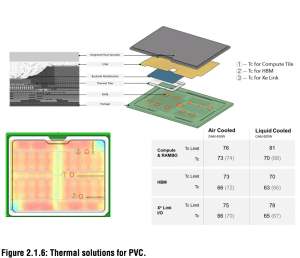

Ранее Intel умалчивала вопрос энергопотребления Ponte Vecchio. FIVR заявлены на 300 Вт для каждого базового тайла. То есть 2x 300 Вт соответствуют 600 Вт для корпусировки в целом. Толстые слои интерконнекта в вычислительных тайлах и в базовом кристалле работают как распределители тепла. Интересно, что вычислительные тайлы сами по себе довольно толстые – 160 мкм. Но тому есть причина, поскольку Intel решила добавить достаточно металлических слоев, чтобы они выдерживали непродолжительные пики Boost.

К 47 активным тайлам (см. таблицу) добавляются 16 термальных тайлов, которые располагаются в тех областях, где базовый тайл не имеет контакта с верхним слоем корпусировки. Термальные тайлы забирают накапливающееся тепло и передают его на распределитель тепла выше. Верхний слой корпусировки представлен Backside Metallization (BSM) вместе с Thermal Interface Material (TIM), знакомым по процессорам. Причем TIM будет компенсировать разницу по толщине. BSM также присутствует на чипах HBM2E и тайлах Xe-Link.

Охлаждать Ponte Vecchio весьма нелегко. Intel указывает TDP 450 Вт для воздушного и 600 Вт для водяного охлаждения. Для компонентов корпусировки заданы температурные диапазоны, в том числе максимальные температуры. Intel говорит о температурах Tc и Tc-Max между 63 и 81 °C – вполне ожидаемые значения в данном сегменте.

Мы пока еще не видели ускорители Ponte Vecchio в работе. Первой платформой для HPC-ускорителя станет суперкомпьютер Aurora. Но ускоритель будет работать и в OEM-системах.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).