Наш коллега Узо Фукузаки (Yuzo Fukuzaki) из TechInsights пролил свет на реализацию AMD 3D V-cache. Технология корпусировки взята у TSMC, она называется TSMC-SoIC. Исследование касается подробностей производства, первые подробности мы уже сообщали во время официальной презентации 3D V-Cache.

Наш коллега Узо Фукузаки (Yuzo Fukuzaki) из TechInsights пролил свет на реализацию AMD 3D V-cache. Технология корпусировки взята у TSMC, она называется TSMC-SoIC. Исследование касается подробностей производства, первые подробности мы уже сообщали во время официальной презентации 3D V-Cache.

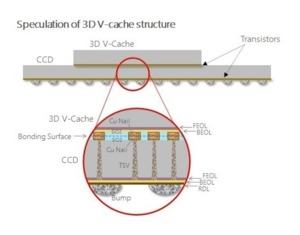

Для 3D V-Cache AMD установила кристалл SRAM площадью 6 x 6 мм напрямую на область кэша L3 CCD. Таким образом, толщина чипа на месте кэша L3 увеличилась. Показанные к данному моменту версии увеличивали кэш 64 MB L3 процессора Ryzen с двумя CCD до 192 Мбайт в сумме, поскольку добавляется 2x 64 MB дополнительного кэша SRAM. В случае процессоров EPYC возможна конфигурация 8x 64 MB дополнительной SRAM. Если стеки SRAM можно будет масштабировать с одного до четырех в обозримом будущем, то емкость дополнительной памяти можно будет тоже увеличить в два, три или даже четыре раза.

Для монтажа кристалла SRAM на CCD, он спиливается на 95% до слоя всего 20 мкм вместо оригинального 400 мкм. В результате оголяются контакты TSV, которые обеспечивают передачу данных и питание SRAM. Речь идет об уровнях 10 и 11 (M10 и M11) из 15 металлических уровней. Если посчитать контакты на CCD, то получается порядка 24.000 TSV, которые выходят с кэша L3 на кристалл SRAM.

Интересно, что сами CCD не производятся с предоставляют TSV, а содержат только контакты Keep Out Zones (KOZ). Затем сверху добавляются TSV. Поскольку TSV и контактные площадки SRAM медные, для удерживания двух кристаллов достаточно физической адгезии, пайка не требуется.

Расстояние между TSV (TSV pitch) составляет всего 17 мкм. Для сравнения, шаг между шариковыми контактами кристалла составляет от 80 до 1xx мкм. Первое и второе поколение технологий корпусировки Intel EMIB (Embedded Multi-die Interconnect Bridge) использует шаг 55 и 45 мкм, соответственно. В случае первого поколения Foveros, где можно соединять кристаллы с разными техпроцессами, шаг составляет 36 мкм. Дальнейшие разработки Foveros Omn и Foveros Direct обеспечат шаг 25 и 10 мкм, соответственно. Поэтому TSMC располагается между двумя вариантами Foveros со своим TSMC SoIC в виде AMD 3D V-Cache.

Будущие процессоры AMD с дизайном чиплетов и 3D V-cache наглядно показывают уровень технических достижений, которые компания смогла получить вместе с TSMC. Дизайн чиплетов обеспечил отличную гибкость в производстве кристаллов и их использовании (CCD с разным числом активных ядер, разным качеством и т.д.). В случае 3D V-Cache AMD делает шаг вперед, добавляя больше кэша при необходимости, что действительно имеет смысл в ряде сценариев. Игровая производительность, например, выигрывает от дополнительного кэша, как продемонстрировала AMD. Серверные процессоры тоже могут использовать дополнительный кэш, будет интересно посмотреть на результаты тестов. AMD планирует представить процессоры с 3D V-Cache в будущем году. Скорее всего, они выйдут на Zen 3 CCD, то есть до перехода на Zen 4.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).