AMD хранила тайну до последнего момента, но на пленарном докладе Computex рассказала о современном состоянии технологии 3D-корпусировки. Несколько дней назад появились слухи о процессоре EPYC с кодовым названием Milan-X, который должен был оснащаться памятью SRAM в стеке. Но, как видим, AMD решила анонсировать данную технологию не с процессорами EPYC, а Ryzen.

AMD хранила тайну до последнего момента, но на пленарном докладе Computex рассказала о современном состоянии технологии 3D-корпусировки. Несколько дней назад появились слухи о процессоре EPYC с кодовым названием Milan-X, который должен был оснащаться памятью SRAM в стеке. Но, как видим, AMD решила анонсировать данную технологию не с процессорами EPYC, а Ryzen.

AMD разработала технологию совместно с TSMC, которая производит важные кристаллы CCD с вычислительными ядрами Zen и GPU для AMD. В распоряжении TSMC имеются различные технологии 3D-корпусировки, и AMD воспользовалась доступным ассортиментом. Доктор Лиза Су упомянула, что технология будет применяться и для грядущих продуктов HPC. Так что появление Milan-X кажется вероятным, как и процессоров Ryzen с 3D V-Cache.

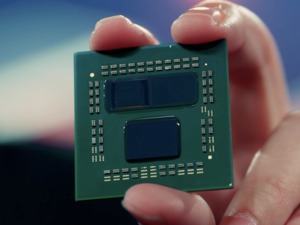

Если верить AMD, речь идет о прототипе процессора Ryzen 5000, который оснащается дополнительным кэшем SRAM 64 Мбайт на CCD. Поскольку AMD выбрала вариант с двумя CCD для своего прототипа, мы получаем 2x 32 Мбайт кэша L3, который уже имеется на CCD, к которому можно добавить 2x 64 Мбайт нового кэша 3D V-Cache.

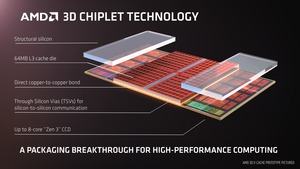

3D V-Cache подключается к кристаллам CCD сквозными проводниками TSV (Through-silicon Via) в 3D-корпусировке. Пропускная способность подключения составляет более 2 Тбайт/с. Дополнительный слой под названием "structural silicon" добавляет высоту там, где 3D V-Cache нет, поэтому толщина CCD остается одинаковой.

На рендеринге показан 3D V-Cache или новые Zen 3 CCD с данной памятью. 3D V-Cache располагается точно над областью CCD, где установлен кэш L3. Области с ядрами Zen 3 не затронуты. То есть слой 3D V-Cache не будет закрывать горячие ядра, чтобы не мешать отведению тепла от них. Structural Silicon обеспечивает оптимальную передачу тепла от ядер на распределитель тепла.

На пленарном докладе Лиза Су показала на камеру прототип процессора. А именно Ryzen 5000 с двумя CCD. Однако для демонстрации отличий только один кристалл CCD оснащен кэшем 3D V-Cache (слева).

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

Вероятно, новая линейка процессоров будет выглядеть следующим образом:

| Кэш L3 | 3D V-Cache | Итого | |

| Ryzen 9 5950X | 64 MB | . | 64 MB |

| Ryzen 9 5950X с 3D V-Cache | 64 MB | 128 MB | 192 MB |

| Ryzen 9 5900X | 64 MB | - | 64 MB |

| Ryzen 9 5900X с 3D V-Cache | 64 MB | 128 MB | 192 MB |

| Ryzen 9 5800X | 32 MB | - | 32 MB |

| Ryzen 9 5800X с 3D V-Cache | 32 MB | 64 MB | 96 MB |

| EPYC 7763 | 256 MB | - | 256 MB |

| EPYC 7763 с 3D V-Cache | 256 MB | 512 MB | 768 MB |

Процессор Ryzen с двумя CCD обеспечит до 128 Мбайт 3D V-Cache, общий объем кэша L3 составит 192 Мбайт. С одним CCD можно рассчитывать на 64 Мбайт 3D V-Cache, то есть в сумме 96 Мбайт. В случае EPYC, то есть Milan-X, мы получим схожую концепцию, разве что объемы кэшей будут отличаться. Процессор EPYC с восемью CCD уже оснащен до 256 Мбайт кэша L3. Новый 3D V-Cache сможет добавить еще 512 Мбайт, что дает 768 Мбайт в сумме. Но пока неизвестно, в каком виде AMD будет оснащать процессоры Ryzen и EPYC новым 3D V-Cache.

Чтобы демонстрировать преимущества 3D V-Cache, AMD представила тест. А именно игру Gears 5, которая запускалась на процессоре Ryzen 9 5950X, после чего на прототипе с 3D V-Cache и 12 ядрами. Оба процессора работали на фиксированной частоте 4 ГГц. Процессор Ryzen 9 5950X смог выдать 184 fps, а Ryzen с 3D V-Cache - 206 fps. AMD говорит о среднем приросте производительности 12% по всем приложениям. Причем в играх прирост составит 15%. Что примерно соответствует приросту IPC при переходе на новую микроархитектуру.

Первые продукты с 3D V-Cache выйдут до конца года. Поэтому вполне вероятно появление процессоров Ryzen Refresh с дополнительной памятью, прежде чем мы получим первые CPU с ядрами Zen 4.

Обновление: AMD ответила на вопросы по поводу 3D V-Cache

После пленарного доклада у нас появилась возможность пообщаться с Самуэлем Нафцигером (Samuel Naffziger) из AMD. Он ответил на несколько вопросов по поводу 3D V-Cache.

Начнем с того, что AMD прояснила ситуацию с выходом первых процессоров Ryzen с 3D V-Cache: они выйдут в конце 2021 года. Пока неизвестно, можно ли их будет купить в 2021 году, либо позднее. В любом случае, подобные процессоры на архитектуре Zen 3 будут доступны в рознице. На данный момент 3D V-cache производится по тому же техпроцессу 7 нм, что и кристаллы CCD, но в оптимизированном варианте, обеспечивающем экстремальную плотность расположения транзисторов.

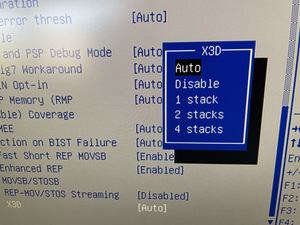

С технической точки зрения интересно сообщение AMD об одиночном слое SRAM, то есть нескольких слоев SRAM на CCD мы пока не увидим. Но 64 Мбайт на одном слое означает, что AMD может добавить еще больше слоев, каждый по 64 Мбайт. Что немаловажно в случае процессоров EPYC, где речь идет уже о четырех слоях.

Влияние на температуры пренебрежимо мало, поскольку тепловыделение кэша SRAM очень невелико. То же самое касается и энергопотребления. Кэш L3, который как раз увеличивается благодаря 3D V-Cache, положительно сказывается на энергопотреблении, поскольку число удачных попаданий растет, что приводит к уменьшению числа операций доступа в оперативную память. Кроме того, существующие Zen 3 CCD уже готовы к добавлению 3D V-Cache, то есть логика управления и питания уже присутствует на CCD. Поэтому 64 MB кэша 3D V-cache и получилось упаковать на площади 36 мм². Чтобы CCD с кэшем 3D V-Cache имел такую же высоту, что и кристалл IOD, он располагается на подложке как можно ниже, сверху устанавливается слой 3D V-Cache.

Что касается задержке 3D V-Cache по сравнению с кэшем L3 CCD, AMD сообщила о небольшом увеличении, но оно не сравнимо с задержками, которые накладываются при доступе к удаленному CCD.

Существующий кэш L3 CCD будет дополняться 3D V-Cache прозрачно для пользователя и приложений. Возможности адресации нового кэша со стороны приложений не предусмотрено.

Обновление 2:

AMD раскрыла новые интересные подробности о 3D V-Cache в эпизоде "The Bring Up".

CCD развернут на 180° и 95% кристалла спилено. Из толщины 400 мкм остаются лишь 20 мкм. И над этим тонким слоем как раз установлен кэш 3D V-Cache. Соединение между CCD и SRAM осуществляется с помощью медных TSV. Как указывает AMD, адгезии медных контактных площадок TSV с двух сторон достаточно для соединения и удерживания двух кристаллов.

Ниже приведены новости AMD на Computex 2021:

- AMD Ryzen 7 5700G и Ryzen 5 5600G появятся в рознице 5 августа

- RDNA 2 в ноутбуках: AMD представила Radeon RX 6800M, 6700M и 6600M

- Работает и на GeForce: FidelityFX Super Resolution выходит 22 июня

- AMD показала процессор Ryzen с 3D V-Cache в стеке

- AMD Advantage: каким требованиям должен соответствовать хороший игровой ноутбук?