Слухи ходили уже давно, но сегодня AMD представила процессоры EPYC с кэшем 3D V-cache. Как и у моделей Ryzen, над областью с кэшем L3 кристалла CCD располагается дополнительный слой SRAM, позволяющий в три раза увеличить емкость L3. В общей сложности доступно 768 Мбайт кэша L3.

Слухи ходили уже давно, но сегодня AMD представила процессоры EPYC с кэшем 3D V-cache. Как и у моделей Ryzen, над областью с кэшем L3 кристалла CCD располагается дополнительный слой SRAM, позволяющий в три раза увеличить емкость L3. В общей сложности доступно 768 Мбайт кэша L3.

Процессоры EPYC с 3D V-cache по-прежнему опираются на архитектуру Zen 3, они разрабатывались под кодовым названием Milan-X. Поэтому и число ядер составляет до 64, процессоры устанавливаются в сокет SP3. Все это упрощает возможности апгрейда, позволяя усилить существующую инфраструктуру. Но перейдем к подробностям.

Во многих сценариях обрабатываемые данные должны располагаться как можно ближе к вычислительным ядрам. Поэтому вместо сравнительно медленной оперативной памяти, гораздо лучше хранить данные в быстром кэше L3. AMD сегодня предлагает процессоры EPYC, содержащие до 256 Мбайт кэша L3. Поэтому здесь позиции компании уже были вполне сильны.

Конечно, 768 Мбайт кэша L3 вместо 256 Мбайт существенно усилят производительность процессора в некоторых областях. Еще одним преимуществом стратегии AMD можно назвать совместимость процессоров EPYC с 3D V-Cache с нынешним сокетом SP3. То есть серверы, которые сегодня работают с третьим поколением процессоров EPYC (Milan), можно легко перевести на процессоры EPYC с кэшем 3D V-Cache (Milan-X).

Каждый CCD уже содержит 32 Мбайт кэша L3, к которым AMD добавляет 64 Мбайт кэша 3D V-cache. То есть на каждом 8-ядерном CCD теперь имеются 96 Мбайт кэша L3. А с восемью CCD на процессор EPYC мы и получаем 768 Мбайт кэша L3. Вероятно, AMD посчитала еще и кэш L2, чтобы показать общий объем 804 Мбайт.

До сих пор AMD демонстрировала только процессоры Ryzen с кэшем 3D V-cache на двух CCD. Он содержал 2x 96 = 192 Мбайт кэша L3 по сравнению с обычным объемом 64 Мбайт.

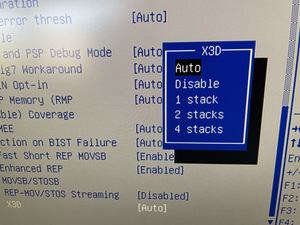

Наш сервер для тестов EPYC третьего поколения уже содержал соответствующие пункты в BIOS, они указывают на дальнейшую работу AMD над несколькими стеками SRAM. Соответственно, емкость L3 может увеличиться до 1.280 и 2.304 MB с двумя и четырьмя стеками. Но вряд ли AMD пойдет на такой шаг с процессорами EPYC на Zen 3. Здесь более вероятными кажутся преемники Genoa (Zen 3) и Trento (Zen 5), которые могут получить несколько стеков.

Прирост производительности от 3D V-Cache очень сильно зависит от сценария использования. Для симуляции Synopsis VCS заявлен 66% прирост скорости верификации (40,6 вместо 24,4 заданий в час). Сравнение проводилось на процессорах EPYC с 16 ядрами, которые оснащались кэшем 3D V-Cache, либо работали без такового (EPYC 73F2).

AMD пока не упоминает конкретных моделей, указывая лишь до 64 ядер. Судя по утечкам, планируются процессоры с 16, 24, 32 и 64 ядрами. Скорее всего, они выйдут в первом квартале 2022. AMD не дает информации и о TDP. Максимальный TDP не изменится, что связано с совместимостью. Но тактовые частоты придется снизить.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).

Скорее всего, ассортимент процессоров будет выглядеть следующим образом:

| Ядра | Базовая частота/Boost | Кэш L3 | TDP | |

| EPYC 7773X | 64 | 2,2 / 3,5 ГГц | 768 Мбайт | 280 Вт |

| EPYC 7763 | 64 | 2,45 / 3,5 ГГц | 256 Мбайт | 280 Вт |

| EPYC 7573X | 32 | 2,8 / 3,6 ГГц | 768 Мбайт | 280 Вт |

| EPYC 7543 | 32 | 2,8 / 3,7 ГГц | 256 Мбайт | 225 Вт |

| EPYC 7473X | 24 | 2,8 / 3,7 ГГц | 768 Мбайт | 240 Вт |

| EPYC 7443 | 24 | 2,85 / 4,0 ГГц | 128 Мбайт | 200 Вт |

| EPYC 7373X | 16 | 3,05 / 3,8 ГГц | 768 Мбайт | 240 Вт |

| EPYC 7343 | 16 | 3,5 / 4,0 ГГц | 128 Мбайт | 240 Вт |

*Официального подтверждения AMD пока нет

Техническая реализация 3D V-Cache

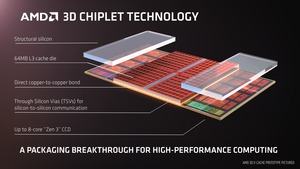

На выставке Computex в начале июня AMD раскрыла подробности кэша 3D V-Cache, в несколько раз увеличивающего кэш L3 процессоров. AMD разрабатывала технологию совместно с TMSC, которая производит CCD для процессоров Zen, а также GPU AMD. Тайваньский производитель предлагает своим клиентам различные технологии корпусировки, и AMD воспользовалась предложением.

Кэш 3D V-cache напрямую подключен к CCD через TSV (Through-Silicon Via), здесь как раз используется технология 3D-корпусировки. Но AMD сначала пришлось спилить 95% толщины кристалла, оставив всего 20 мкм от 400 мкм. Кэш 3D V-cache, который имеет площадь 36 мм², как раз устанавливается вместо спиленного слоя. На конференции HotChips AMD раскрыла ряд подробностей производства 3D V-Cache. Среди них - расстояние между TSVs (Through-Silicon Via), обеспечивающими физическое подключение SRAM, составляет всего 9 мкм.

Поскольку TSV и контактные площадки SRAM медные, для удерживания двух кристаллов достаточно физической адгезии, пайка не требуется. Скорость передачи данных составляет более 2 Тбайт/с. Там, где кэша 3D V-cache нет, добавляется слой "Structural Silicon", что позволяет выровнять толщину кристалла CCD.

Таким образом, 3D V-cache располагается точно над областью L3-кэша CCD. Области с ядрами Zen 3 не затрагиваются. Идея разумная, поскольку 3D V-cache не закрывает горячие ядра. Тепло на распределитель от ядер передается слоем Structural Silicone.

Процессоры Ryzen с кэшем 3D V-Cache тоже ожидаются в первом квартале 2022. AMD для них не приводит конкретные результаты производительности, говоря лишь о среднем приросте 12% по всем приложениям. В играх прирост составит 15%. Здесь AMD надеется контратаковать процессоры Intel Alder Lake, которые получили существенный прирост игровой производительности.