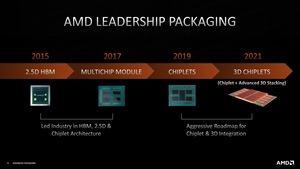

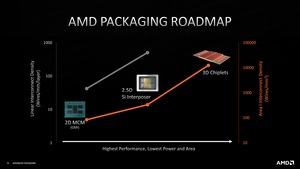

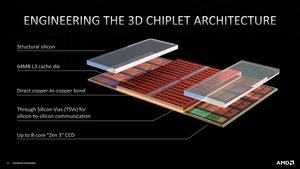

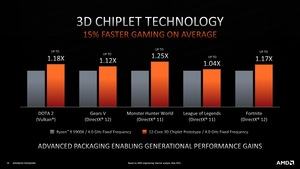

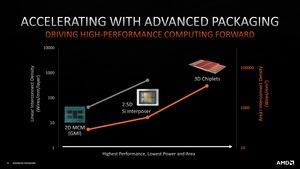

На выставке Computex в начале июня AMD раскрыла подробности 3D V-Cache, который в многократно увеличивает кэш L3 процессоров. На первом этапе AMD планирует увеличить кэш L3 каждого CCD в три раза. Подобный прирост стал возможным благодаря добавлению новых стеков. 3D V-Cache - решение AMD, удовлетворяющее потребности современных систем, которым нужна более емкая и быстрая память как можно ближе к ядрам CPU.

На выставке Computex в начале июня AMD раскрыла подробности 3D V-Cache, который в многократно увеличивает кэш L3 процессоров. На первом этапе AMD планирует увеличить кэш L3 каждого CCD в три раза. Подобный прирост стал возможным благодаря добавлению новых стеков. 3D V-Cache - решение AMD, удовлетворяющее потребности современных систем, которым нужна более емкая и быстрая память как можно ближе к ядрам CPU.

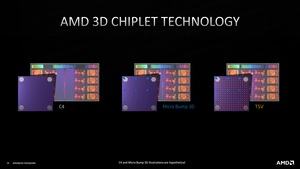

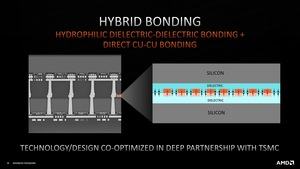

AMD производит процессоры не сама, разработка кэша 3D V-Cache тоже выполнялась совместно с TSMC. Тайваньский производитель как раз предлагает своим клиентам технологию корпусировки TSMC-SoIC.

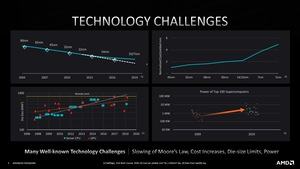

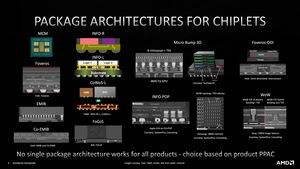

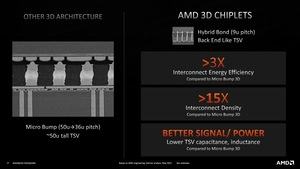

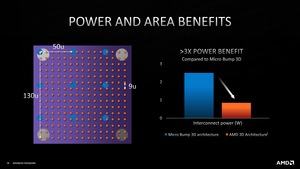

AMD в рамках конференции Hot Chips 33 раскрыла некоторые подробности 3D V-Cache. Презентацию прочитал Раджа Сваминатан, старший сотрудник AMD, отвечающий за технологии корпусировки. Кроме прочего, Раджа рассказал о расстоянии между связями TSVs (Through-Silicon Via). Наши коллеги TechInsights ранее предположили расстояние 17 мкм. Для сравнения: технология корпусировки Intel EMIB (Embedded Multi-die Interconnect Bridge) первого и второго поколения дает 55 и 45 мкм, соответственно. У первого поколения Foveros, объединяющей чипы разных техпроцессов, расстояние снижено до 36 мкм. Дальнейшие разработки Foveros Omni и Foveros Direct должны обеспечить расстояние 25 и 10 мкм, соответственно. И в случае 17 мкм AMD совместно с TSMC смогла добиться просто отличных результатов.

Если же верить презентации, AMD для 3D V-cache вообще смогла сократить расстояние между TSVs всего до 9 мкм. Что позиционирует технологию на уровне Foveros Direct - нового поколения корпусировки Intel, которым чиповый гигант очень гордится. Похоже, что TSMC здесь ничем не уступает.

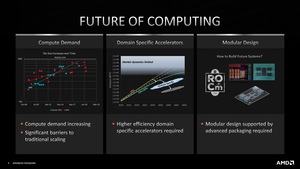

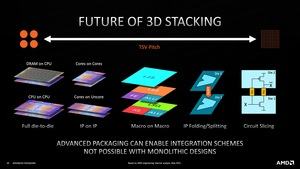

Впрочем, 3D V-Cache - это лишь первый шаг в планах AMD по 3D-корпусировке. На следующем этапе можно ожидать не только добавление кэша, но также установку DRAM напрямую на ядра CPU. В будущем AMD планирует устанавливать друг на друга и ядра CPU. AMD рассматривает варианты "CPU on CPU", то есть процессор на процессоре, а также расположение ядер на области Uncore (Cores on Uncore). Intel уже делает что-то похожее с Lakefield. "Macro on Macro" означает преобразование функциональных блоков ядер в 3D-структуру. Здесь интересно оценить, какой вклад вносят задержки при использовании связей TSV.

Следующий уровень - стеки из разных областей IP или даже отдельных схем. Таким образом, можно добиться практически бесконечного числа слоев, которые обеспечат свои преимущества на практике. Впрочем, все, начиная от "Macro on Macro", пока находится в далеком будущем. Первая проблема (после производства чипов и корпусировки) заключается в охлаждении. И охлаждать чипы DRAM на ядрах или CPU на CPU будет весьма непросто. Впрочем, TSMC уже работает над вариантами решения.

Подписывайтесь на группы Hardwareluxx ВКонтакте и Facebook, а также на наш канал в Telegram (@hardwareluxxrussia).