В ходе сессии вопросов и ответов генерального директора Intel Пэта Гелсингера спросили, работает ли Intel над технологией, подобной 3D V-Cache от AMD. Ответ был положительный, но в последние часы появились многочисленные сообщения, в которых мы хотим разобраться подробнее.

В ходе сессии вопросов и ответов генерального директора Intel Пэта Гелсингера спросили, работает ли Intel над технологией, подобной 3D V-Cache от AMD. Ответ был положительный, но в последние часы появились многочисленные сообщения, в которых мы хотим разобраться подробнее.

Ответ Пэта Гелсингера был следующим:

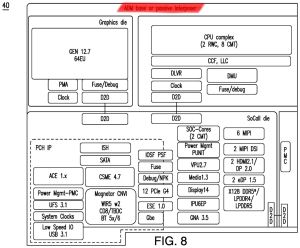

Слухи о расширенном кэше в базовом тайле Meteor Lake не новы. Однако Intel, очевидно, решила отказаться от такого дополнительного кэша в пользу следующего поколения. Intel получила соответствующий патент, в котором изображен процессор Meteor Lake с пассивной подложкой, как описано в статье, либо с подложкой Adamantine. Насколько большим мог бы стать этот кэш L4, пока точно неизвестно. По слухам, Intel тестировала Meteor Lake с объемом кэша от 128 до 512 Мбайт.

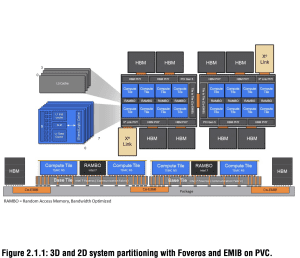

Впрочем, размещение SRAM в подложке - идея не новая, она даже реализована Intel. Именно на это и ссылается Гелсингер в своем ответе. В базовом тайле Ponte Vecchio предусмотрено 144 Мбайт кэша L2. Тайлы с вычислительными ядрами, кэш-памятью Rambo и Xe-Link как раз расположены поверх базового тайла.

Аналогичная картина может быть реализована для Arrow Lake, а теперь потенциально и для Lunar Lake и последующих поколений. Есть и существенное отличие в реализации: если AMD размещает 3D V-кэш в виде SRAM поверх вычислительного чиплета, то Intel устанавливает дополнительный кэш в базовом тайле, а вычислительные тайлы располагает сверху. Судя по всему, серьезных проблем с охлаждением не возникает, иначе технология не была бы реализована в таком виде для Ponte Vecchio.

Однако возникает вопрос: если в Ponte Vecchio SRAM использовалась как кэш-память L2, то в патенте Adamantine она описывается как кэш-память L4. Однако уровни кэша имеют принципиальное значение для его использования. Ядра процессора не смогут воспользоваться преимуществами кэша L4 таким же образом, как кэшами L2 или L3. AMD за счет 3D V-Cache расширила кэш L3, что благоприятно сказалось на производительности процессоров Ryzen X3D, особенно в играх.

Так что в каком виде мы увидим стековую память у Intel в клиентском сегменте, пока неизвестно. Впрочем, любая реализация уже не станет большим сюрпризом.

Подписывайтесь на группу Hardwareluxx ВКонтакте и на наш канал в Telegram (@hardwareluxxrussia).