Страница 3: Архитектура Vega в подробностях - часть 2

High Bandwidth Cache Controller

High Bandwidth Cache Controller (HBCC) довольно важен для эффективного использования памяти HBM2, он управляет хранением данных в кэше HB (как AMD называет видеопамять на видеокартах Vega), в оперативной памяти и на накопителях (SSD). В общей сложности HBCC может управлять виртуальным адресным пространством до 512 Тбайт. Все GPU в системе могут использовать общую память с 49-битной адресацией. Для этой цели создаются пулы памяти. Теоретически физическая память может составлять до 256 Тбайт.

Вместе с HBCC AMD представляет управление памятью на основе страниц - Page Based Memory Management. Данные больше не представляются крупными непрерывными областями в памяти, а разделяются на страницы. Работать с небольшими страницами можно быстрее, неиспользуемые данные можно переносить из быстрой памяти HBM2 в менее быструю. Если посмотреть на распределение данных в видеопамяти, то только порядка 50% из них активно используются GPU.

Если игровой движок не берет на себя задачу управления видеопамятью, ею может заниматься HBCC, часто используемые страницы остаются в быстрой памяти, также выставляются приоритеты страниц. Размер страниц может меняться, все зависит от данных. AMD указывает размеры страниц 2 MB, 1 MB, 512 KB, 256 KB, ... и так далее.

Однако это отнюдь не означает, что все видеокарты Radeon RX Vega штатно будут работать через HBCC. Современные стандарты предусматривают управление распределением памяти со стороны игровых движков. То есть AMD не сможет взять эту задачу на драйвере и передать HBCC. Подсистема HBCC начнет работать, только если разработчики напрямую укажут ее поддержку в игре. Стандартный случай без HBCC AMD называет Exclusive Cache Mode. В режиме Inclusive Cache Mode контроллер HBCC уже отвечает за распределение данных по HBM2 и другим видам памяти.

На Radeon RX Vega с 8 Гбайт HBM2 в экстремальных случаях возможно выделение до 27 Гбайт адресного пространства, что позволяет в реальном времени хранить до 500 млн. полигонов и работать с ними. Пользователь в драйвере может выделить виртуальную память, сочетающую 8 Гбайт HBM2 и доступную память системы. Остальное обеспечит контроллер HBCC.

Draw Stream Binning Rasterizer

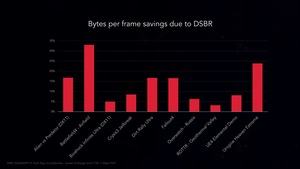

Блок Pixel Engine тоже был улучшен. Теперь он поддерживает технологию Draw Stream Binning Rasterizer, обеспечивающую лучший уровень сжатия данных. Технология снижает требования к пропускной способности видеопамяти, что также дает преимущества по скорости передачи данных в память или обратно. На сцене расчет идет по объектам, которые могут быть видимы для растеризатора или нет. Алгоритм Draw Stream Binning Rasterizer позволяет скрыть пиксели объекта, которые остаются невидимыми. И выполнять для них затенение больше не требуется. Все это позволяет уменьшить потребляемое пространство в памяти и пропускную способность памяти. В предыдущих архитектурах GPU AMD пиксельная и текстурная память не были синхронизированы, поэтому часто возникали дубли. В случае архитектуры Vega Geometry Pipeline, Compute Engine и Pixel Engine используют доступны кэши L1 и L2 совместно. То же самое касается и задней части конвейера рендеринга.

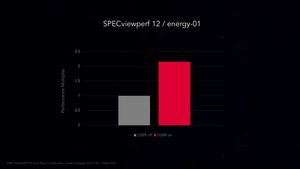

Использование Draw Stream Binning Rasterizer может существенно увеличить производительность в некоторых сценариях. В частности, путем отказа от вычислений, если определяются дубли/наложения. AMD привела результаты собственных тестов.

Display Engine

В архитектуре Vega был немного изменен движок дисплеев (Display Engine). Впрочем, не стоит ожидать существенного продвижения вперед с поддержкой новых стандартов, как это было в случае предыдущих архитектур.

DisplayPort 1.4 на видеокартах Vega теперь поддерживает расширенное цветовое пространство HBR3, MST для HDR. Через HDMI 2.0 поддерживается разрешение UHD с частотой обновления 60 Гц и 12-битным HDR, с кодированием 4:2:0. На всех выходах DisplayPort и HDMI поддерживаются HDCP 2.2 и FreeSync.

Число выходов на дисплеи, которые можно одновременно использовать с определенными разрешениями, тоже увеличилось.